# ARMY TM 11-6625-3241-40 MARINE CORPS TM 09045B-40/2

## **TECHNICAL MANUAL**

# GENERAL SUPPORT MAINTENANCE MANUAL FOR

OSCILLOSCOPE OS-291/G

(TEKTRONIX MODEL 2430A)

(NSN 6625-01-258-0022)

Distribution is authorized to Department of Defense and DOD contractors only for official use or for administration or operational purposes. This determination was made on 27 August, 1988. Other requests for this document will be referred to Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-LC-LM-LT, Fort Monmouth, NJ 07703-5000.

**DESTRUCTION NOTICE** – Destroy by any method that will prevent disclosure of contents or reconstruction of the document.

HEADQUARTERS, DEPARTMENT OF THE ARMY

1 MARCH 1991

(This manual includes copyright material reproduced by permission of TEKTRONIX, Inc.)

Technical Manual No. 11-6625-3241-40 Technical Manual No. 09045B-40/2 DEPARTMENT OF THE ARMY AND HEADQUARTERS, MARINE CORPS Washington, DC, 1 March 1991

# GENERAL SUPPORT MAINTENANCE MANUAL FOR

# OSCILLOSCOPE OS-291/G (TEKTRONIX MODEL 2430A) (NSN 6625-01-258-0022)

## REPORTING ERRORS AND RECOMMENDING IMPROVEMENTS

You can help improve this manual. If you find any mistakes or if you know of a way to improve the procedures, please let us know. Mail your letter, DA Form 2028 (Recommended Changes to Publications and Blank Forms), or DA Form 2028-2 located in the back of this manual direct to: Commander, U.S. Army Communication-Electronics Command, ATTN: AMSEL-LC-LM-LT, Fort Monmouth, New Jersey 07703-5000. Marine Corps units, submit NAVMC 10772 (Recommended Changes to Technical Publications) to: Commanding General, Marine Corps Logistics Base (Code 850) Albany, Georgia 31704-5000. In either case, a reply will be furnished to you.

This manual is an authentication of the manufacturer's commercial literature which, through usage, has been found to cover the data required to operate and maintain this equipment. Since the manual was not prepared in accordance with military specifications, the format has not been structured to consider levels of maintenance.

## TABLE OF CONTENTS

| SECTION 0 | INTRODUCTION                                                  |

|-----------|---------------------------------------------------------------|

|           | Scope                                                         |

|           | Consolidated Index of Army Publications and Blank Forms       |

|           | Maintenance Forms, Records, and Reports                       |

|           | Reporting Equipment improvement Recommendations (EIR)         |

|           | Administrative Storage                                        |

|           | Destruction of Army Electronics Materiel to Prevent Enemy Use |

| SECTION 1 | SPECIFICATION                                                 |

|           | Introduction                                                  |

|           | Vertical System                                               |

|           | Horizontal System                                             |

|           | Trigger System                                                |

|           | Cursor Measurements                                           |

|           | Waveform Acquisition                                          |

|           | Storage and I/O                                               |

|           | Extended Features                                             |

|           | Performance Conditions                                        |

|           | Recommended Adjustments Schedule                              |

| SECTION 2 | PREPARATION FOR USE                                           |

|           | Safety                                                        |

|           | Line Voltage Selection                                        |

|           | Line Fuse                                                     |

|           | Power Cord                                                    |

|           | Instrument Cooling                                            |

|           | Start-up                                                      |

|           | Power-down                                                    |

|           | Repackaging For Shipment                                      |

| SECTION 3 | THEORY OF OPERATION                                           |

|           | Section Organization                                          |

|           | integrated Circuit Descriptions                               |

|           | Simplified Block Diagram Description                          |

|           | Detailed Block Diagram Description                            |

|           | introduction                                                  |

|           | input Signal Conditioning and Analog Sampling                 |

|           | Acquisition Process and Control                               |

## TABLE OF CONTENTS-CONT

|           |                                                           | Page |

|-----------|-----------------------------------------------------------|------|

| SECTION 3 | THEORY OF OPERATION-CONT                                  |      |

|           | Detailed Block Diagram Description-CONT                   |      |

|           | Data Clocking to Acquisition Memory                       | 3-10 |

|           | Analog Data Conditioning and A/D Conversion               | 3-11 |

|           | Acquisition Processing and Display                        | 3-12 |

|           | Detailed Circuit Description                              | 3-14 |

|           | System Processor                                          | 3-14 |

|           | Waveform Processor System.,                               | 3-21 |

|           | Front Panel Processor                                     | 3-26 |

|           | Front Panel                                               | 3-28 |

|           | System DAC And Acquisition Control Registers              | 3-29 |

|           | System DAC (Cont) and Auxiliary Front Panel               | 3-31 |

|           | System Clocks                                             | 3-32 |

|           | Time Base Controller and Acquisition Memory               | 3-36 |

|           | Attenuators and Preamps                                   | 3-40 |

|           | Peak Detectors and CCD/Clock Drivers                      | 3-42 |

|           | Triggers and Phase Clocks                                 | 3-47 |

|           | Jitter Correction Ramps                                   | 3-52 |

|           | Trigger Holdoff, Jitter Counters, and Calibrator          | 3-53 |

|           | CCD Output                                                | 3-56 |

|           | A/D Converter and Acquisition Latches                     | 3-57 |

|           | Display and Attributes Memory                             | 3-59 |

|           | Display Control                                           | 3-61 |

|           | Display Output                                            | 3-67 |

|           | High-Voltage Supply and CRT                               | 3-70 |

|           | System I/O                                                | 3-74 |

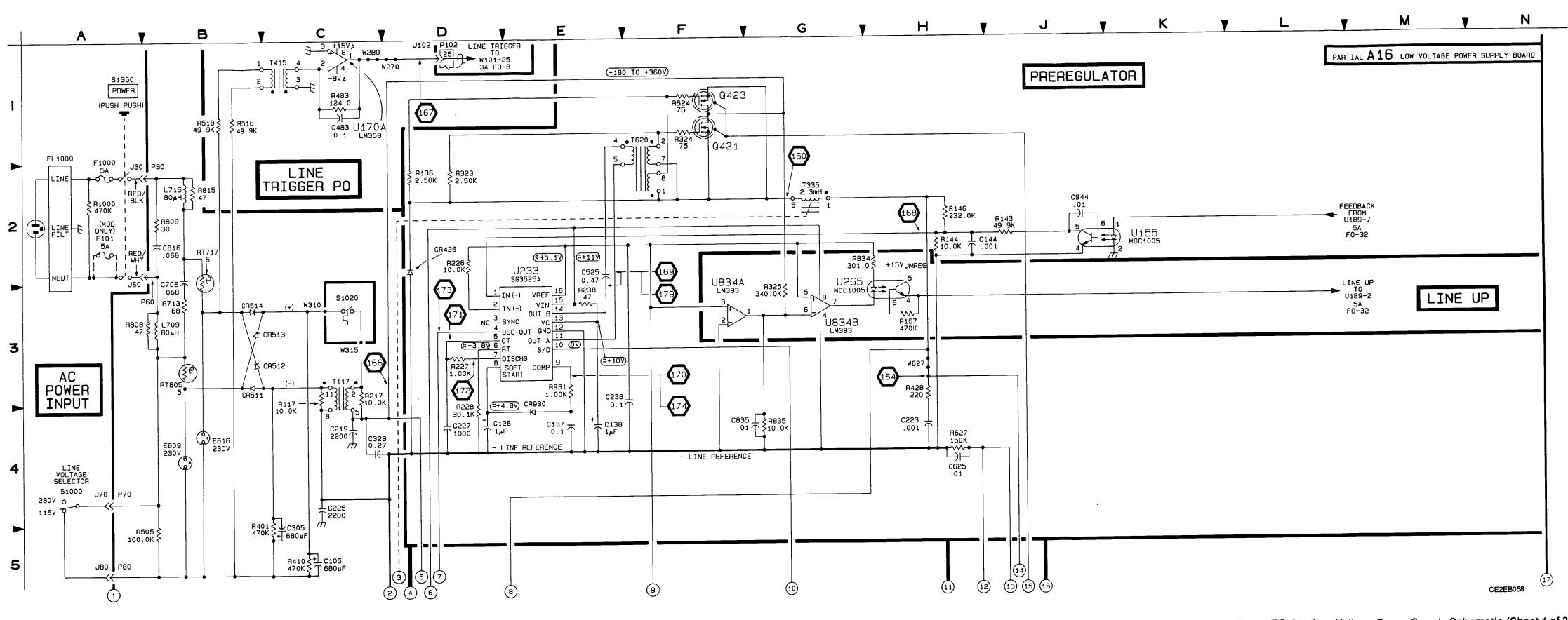

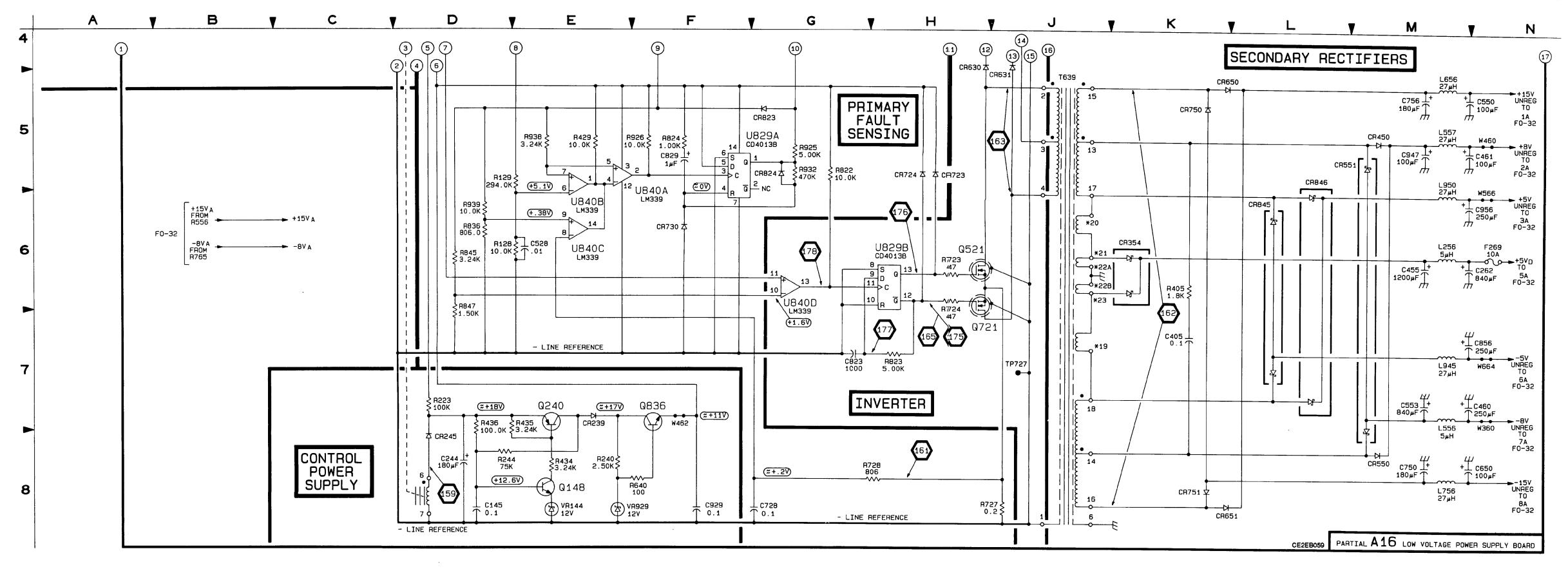

|           | Low-Voltage Power Supply                                  | 3-77 |

|           | Low-Voltage Regulators                                    | 3-82 |

| SECTION 4 | PERFORMANCE CHECK AND FUNCTIONAL VERIFICATION PROCEDURE . | 4-1  |

|           | Introduction                                              | 4-1  |

|           | Preparation                                               | 4-1  |

|           | Initial Setup                                             | 4-3  |

|           | Vertical System                                           | 4-5  |

|           | Triggering Systems                                        | 4-14 |

|           | Horizontal System                                         | 4-21 |

|           | Additional Verifications and Checks                       | 4-24 |

## TABLE OF CONTENTS-CONT

|           |                                             | Pag  |

|-----------|---------------------------------------------|------|

| SECTION 5 | ADJUSTMENT PROCEDURE                        | 5-1  |

|           | Introduction                                | 5-1  |

|           | Calibration Sequence and Partial Procedures | 5-1  |

|           | Warm-up Time Requirements                   | 5-1  |

|           | Preservation of Instrument Calibration      | 5-2  |

|           | Internal Adjustments                        | 5-3  |

|           | Self Calibration                            | 5-10 |

| SECTION 6 | MAINTENANCE                                 | 6-1  |

|           | Instrument Calibration                      | 6-1  |

|           | National Bureau of Standards Traceability   | 6-2  |

|           | Voiding Calibration                         | 6-2  |

|           | Static-sensitive Components                 | 6-3  |

|           | Preventive Maintenance                      | 6-4  |

|           | Introduction                                | 6-4  |

|           | General Care                                | 6-4  |

|           | inspection and Cleaning                     | 6-4  |

|           | Lubrication                                 | 6-6  |

|           | Semiconductor Checks                        | 6-6  |

|           | Periodic Readjustment                       | 6-6  |

|           | Troubleshooting                             | 6-7  |

|           | Introduction                                | 6-7  |

|           | Troubleshooting Aids                        | 6-7  |

|           | Troubleshooting Equipment                   | 6-8  |

|           | Troubleshooting Techniques                  | 6-8  |

|           | Corrective Maintenance                      | 6-11 |

|           | Introduction                                | 6-11 |

|           | Maintenance Precautions                     | 6-11 |

|           | Selectable Components                       | 6-11 |

|           | Maintenance Aids                            | 6-11 |

|           | Interconnections                            | 6-11 |

|           | Transistors and integrated Circuits         | 6-13 |

|           | Soldering Techniques                        | 6-13 |

|           | Removal and Replacement Procedure           | 6-14 |

## TABLE OF CONTENTS-CONT

| SECTION 6  | MAINTENANCE-CONT                              |        |

|------------|-----------------------------------------------|--------|

|            | Internal Diagnostics and Calibration Routines | 6-23   |

|            | Introduction                                  | 6-23   |

|            | Overview                                      | 6-23   |

|            | Calibration Routines                          | 6-23   |

|            | Diagnostic Routines                           | 6-25   |

|            | Diagnostics Operation via the GPIB Interface  | 6-31   |

|            | Diagnostic Procedures                         | 6-32   |

|            | Front Panel Settings for Init Panel           | 6-97   |

| APPENDIX A | REFERENCES                                    | A-1    |

| APPENDIX B | EXPENDABLE SUPPLIES AND MATERIALS LIST        | B-1    |

| INDEX      |                                               | Index- |

## LIST OF ILLUSTRATIONS

| Number | Title                                                                                       | Page |

|--------|---------------------------------------------------------------------------------------------|------|

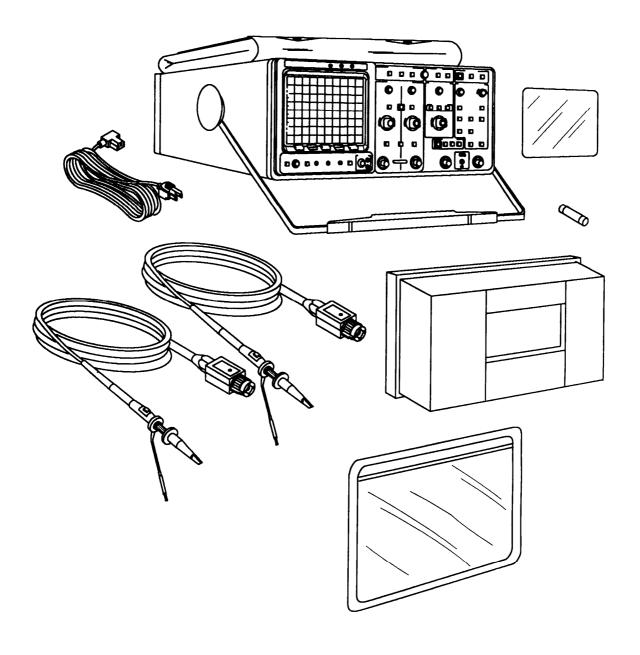

| 1-1    | Oscilloscope OS-291/G                                                                       | 1-0  |

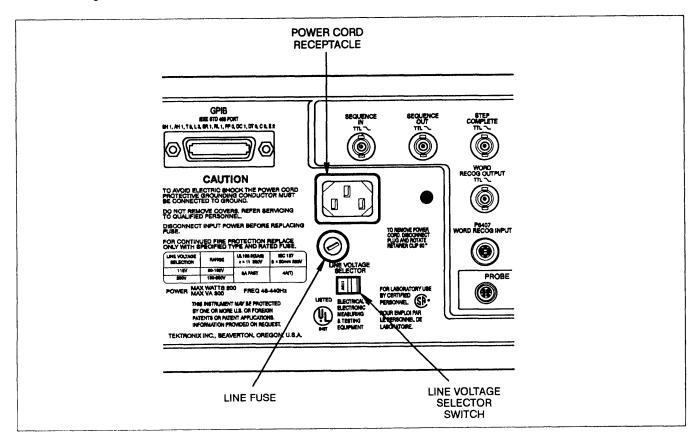

| 2-1    | LINE VOLTAGE SELECTOR, line fuse, and power cord receptacle                                 | 2-1  |

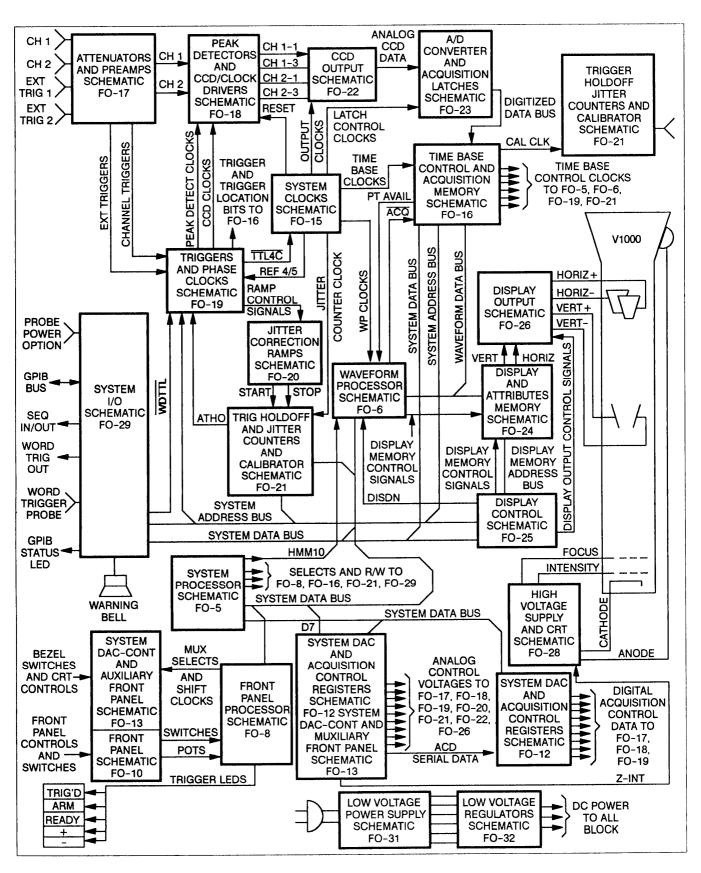

| 3-1    | Oscilloscope OS-291/G simplified block diagram                                              | 3-3  |

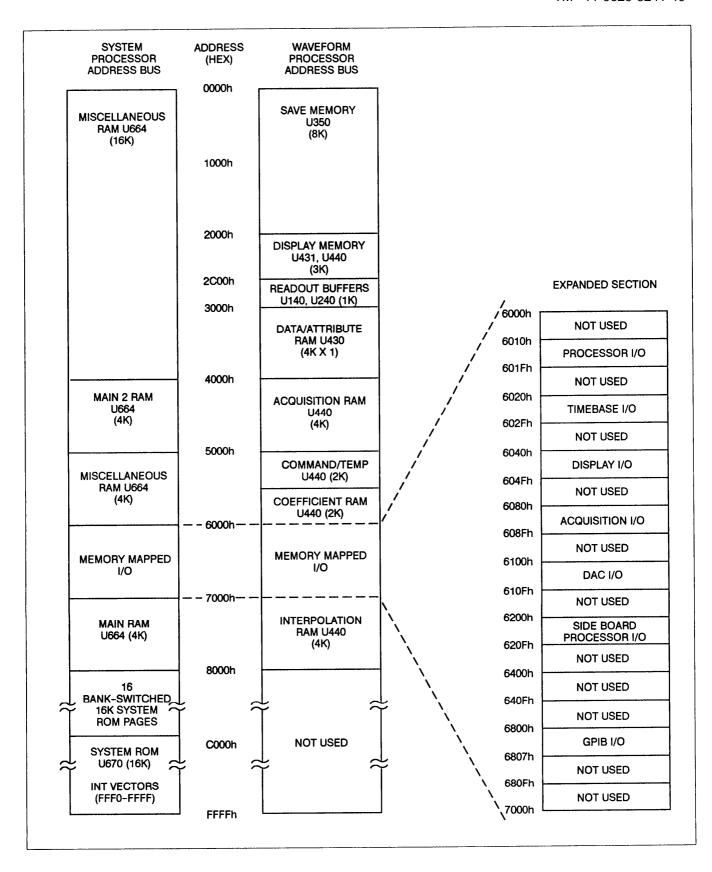

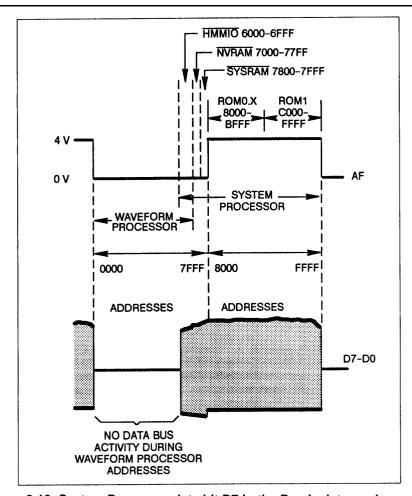

| 3-2    | Simplified Memory Map of the OS-291/G                                                       | 3-17 |

| 3-3    | System Clock waveforms                                                                      | 3-34 |

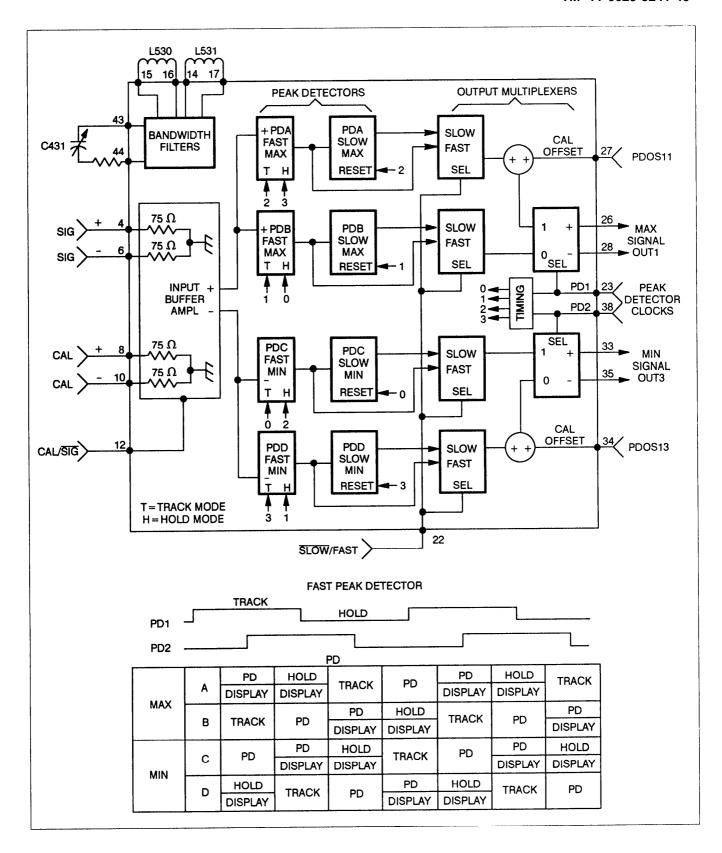

| 3-4    | Simplified Peak Detector block diagram                                                      | 3-43 |

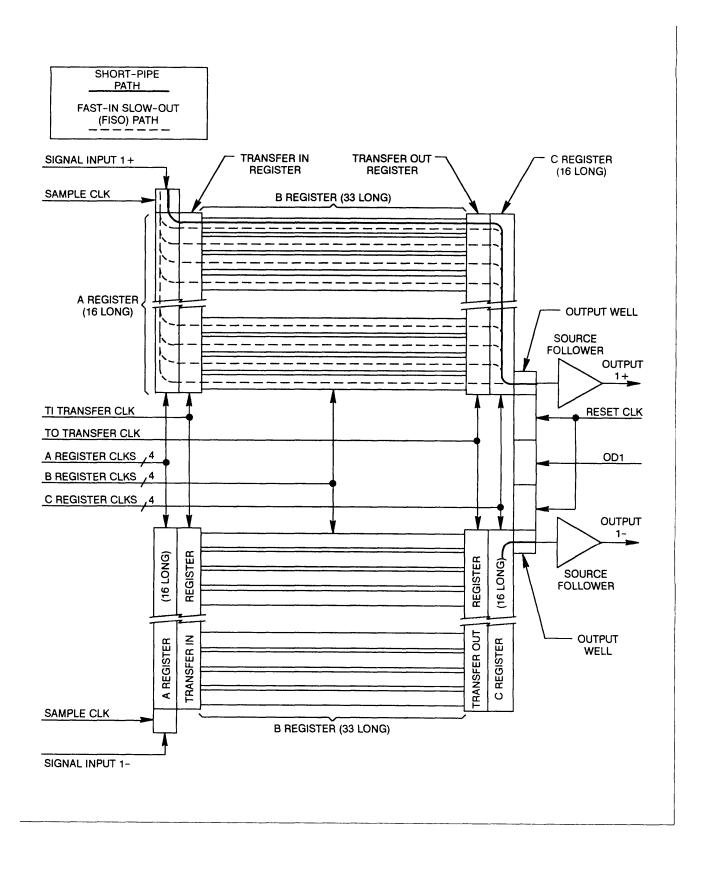

| 3-5    | Simplified CCD architecture                                                                 | 3-46 |

| 3-6    | Trigger Logic Array Control Data Byte                                                       | 3-49 |

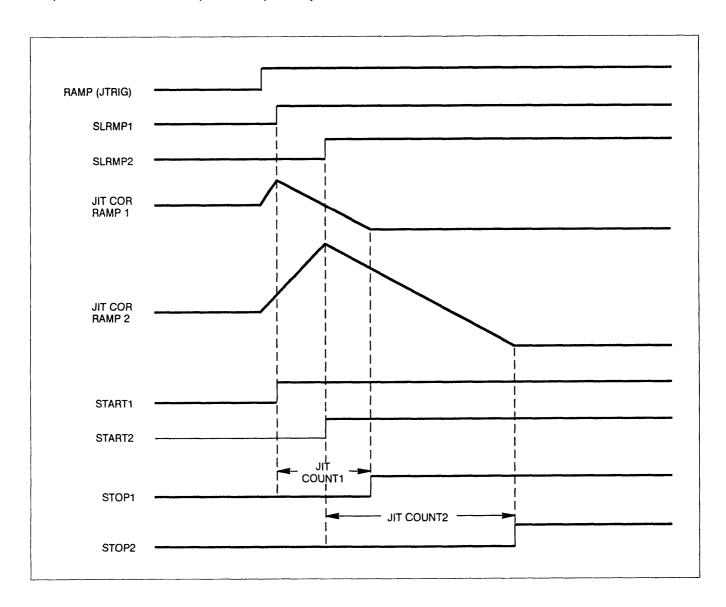

| 3-7    | Jitter correction waveforms                                                                 | 3-53 |

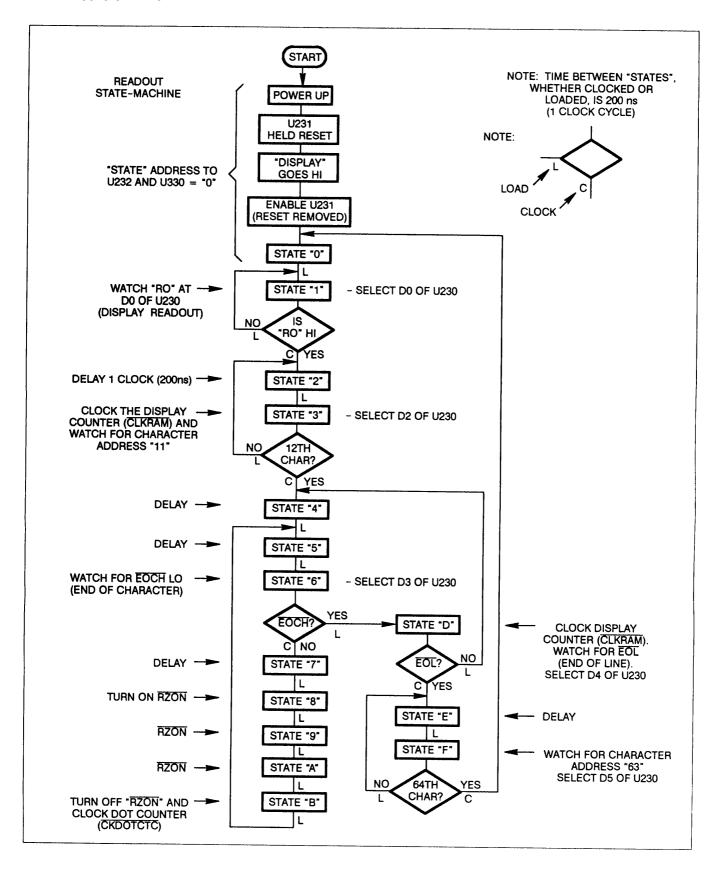

| 3-8    | Readout State Machine flow chart                                                            | 3-66 |

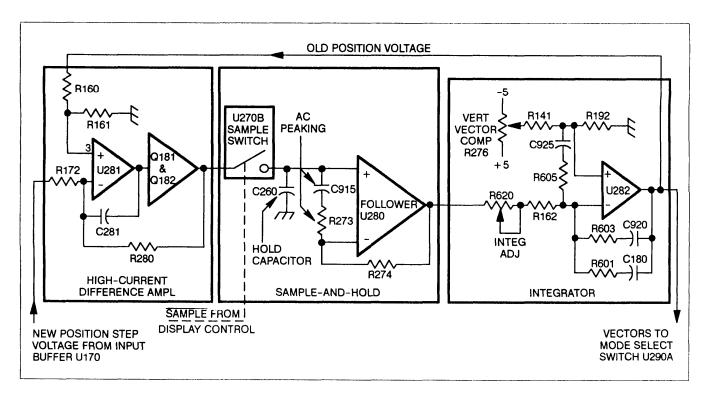

| 3-9    | Vertical Vector Generator                                                                   | 3-68 |

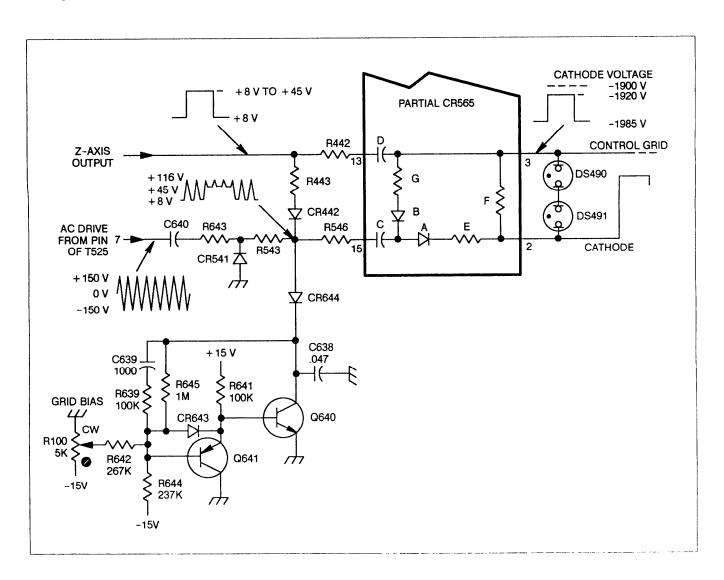

| 3-10   | DC Restorer                                                                                 | 3-72 |

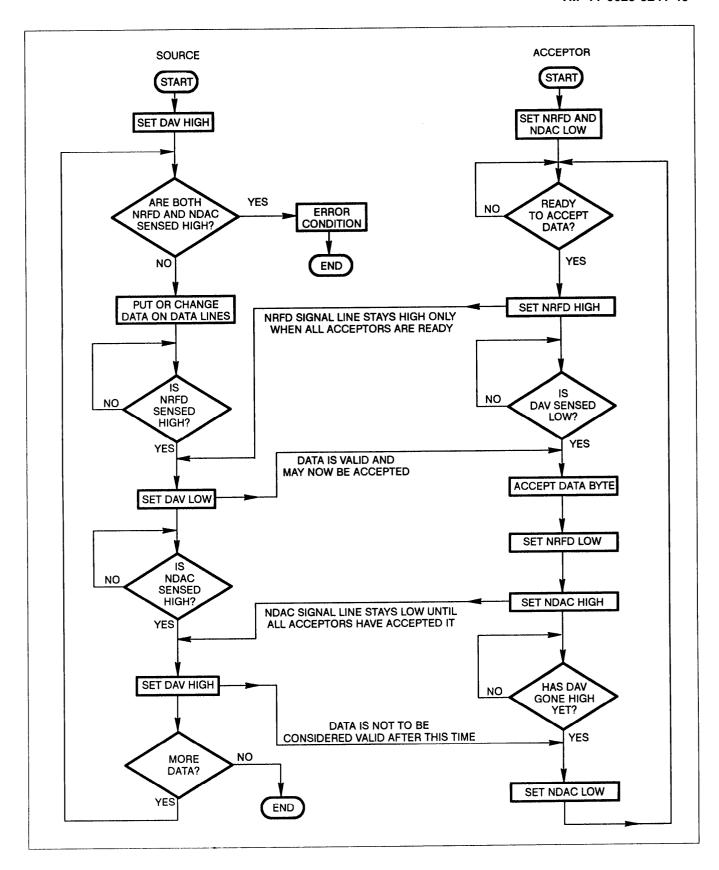

| 3-11   | GPIB data flow diagram                                                                      | 3-75 |

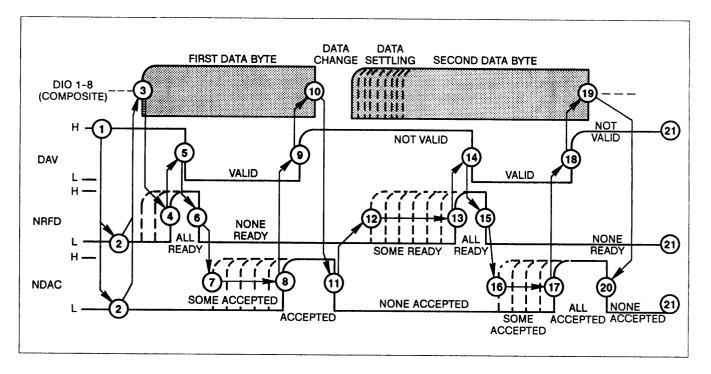

| 3-12   | GPIB three-wire handshake state diagram                                                     | 3-76 |

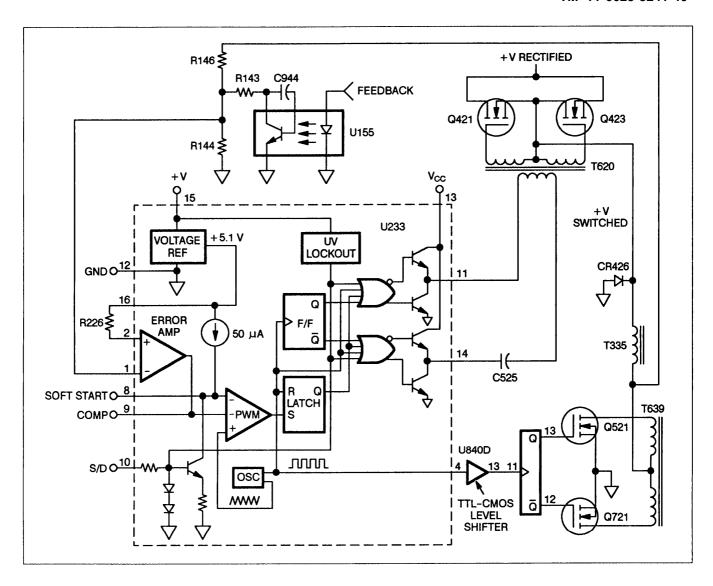

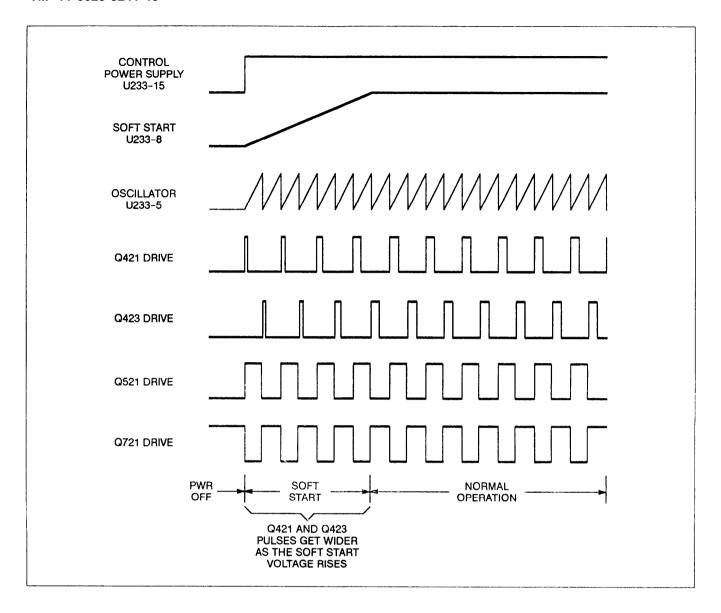

| 3-13   | PWM Regulator and Inverter                                                                  | 3-79 |

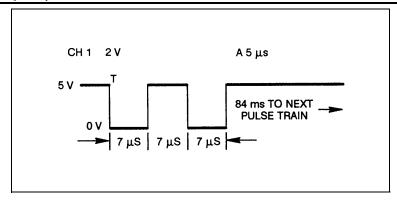

| 3-14   | PWM switching waveforms                                                                     | 3-80 |

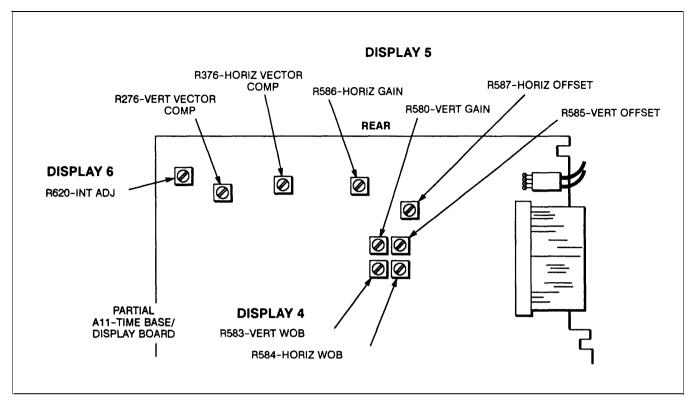

| 5-1    | Adjustment locations for Displays 4 through 6                                               | 5-4  |

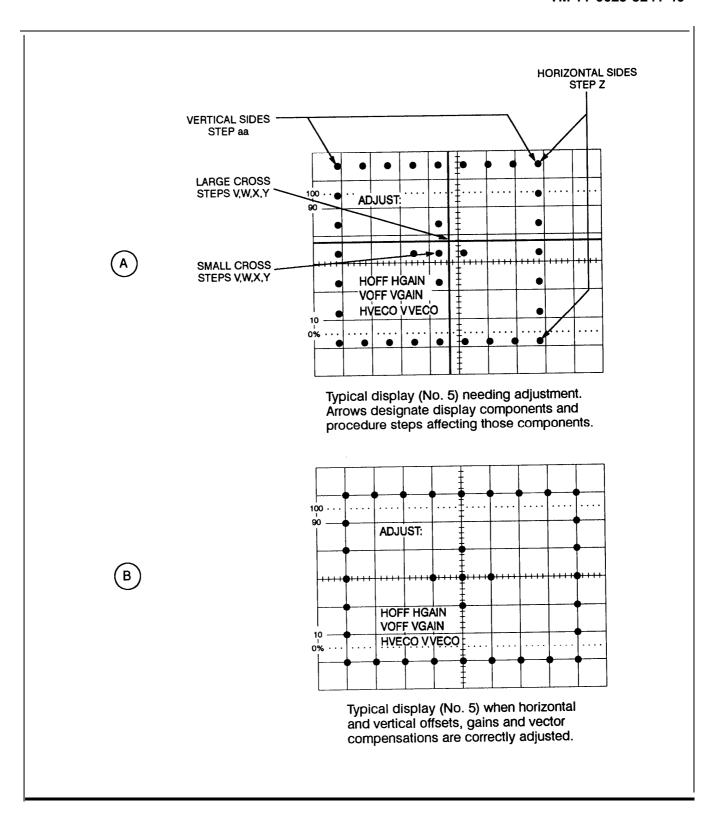

| 5-2    | Display 5–Vertical and Horizontal Gain, Offset, and Vector Compensation adjustments pattern | 5-5  |

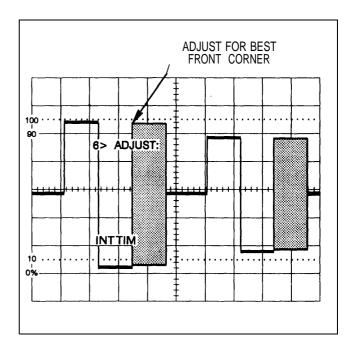

| 5-3    | Integrator Time adjustment pattern                                                          | 5-6  |

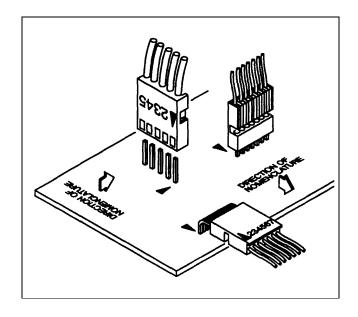

| 6-1    | Multipin connector                                                                          | 6-8  |

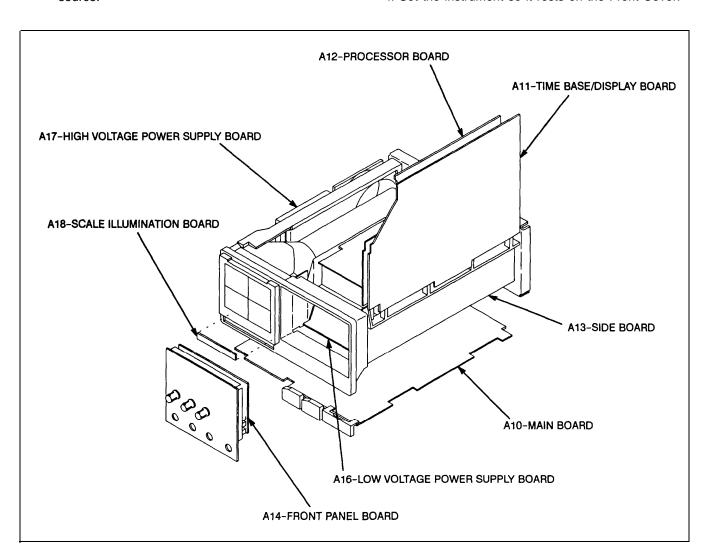

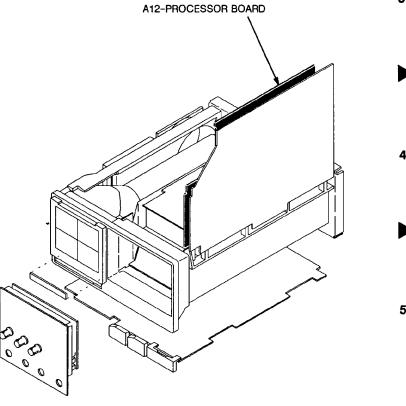

| 6-2    | Circuit Board Location                                                                      | 6-15 |

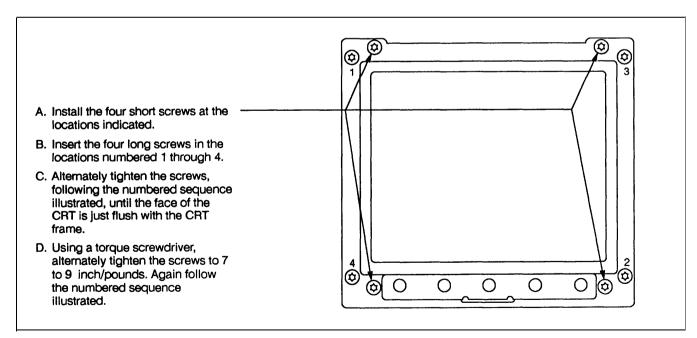

| 6-3    | Installation sequence for installing the CRT frame screws                                   | 6-21 |

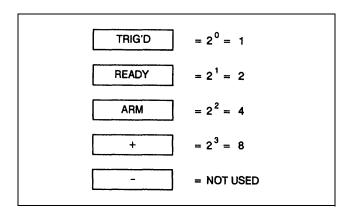

| 6-4    | Trigger LED binary coding for diagnostic tests                                              | 6-26 |

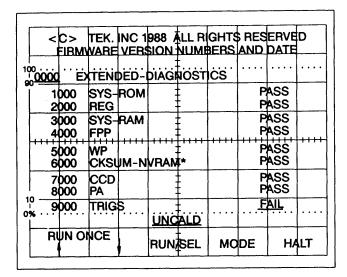

| 6-5    | Main EXT DIAG menu                                                                          | 6-27 |

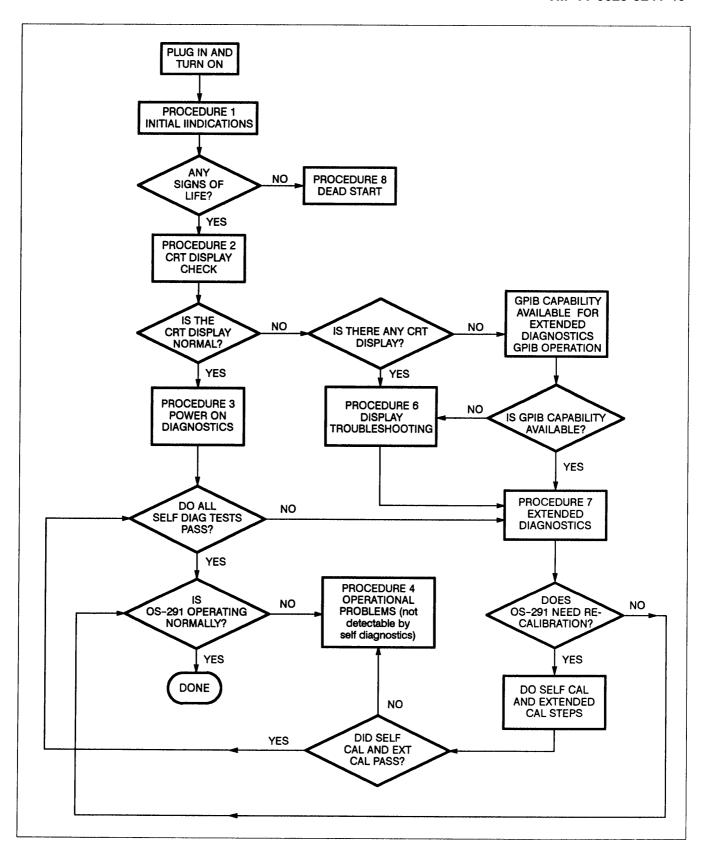

| 6-6    | Initial Troubleshooting Chart                                                               | 6-33 |

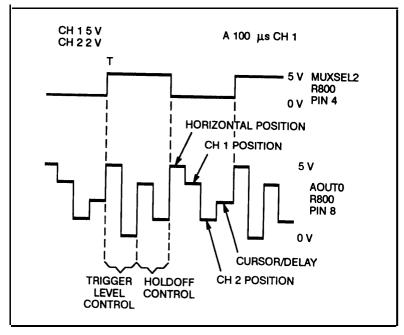

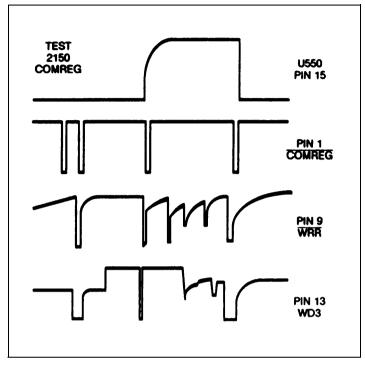

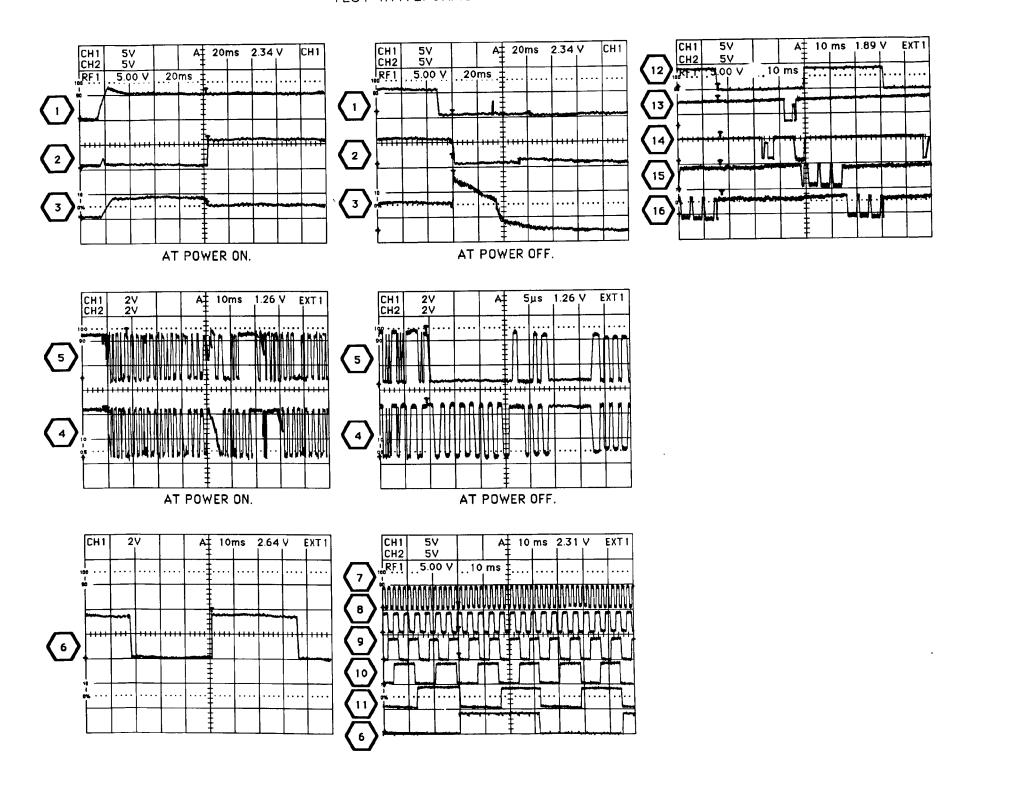

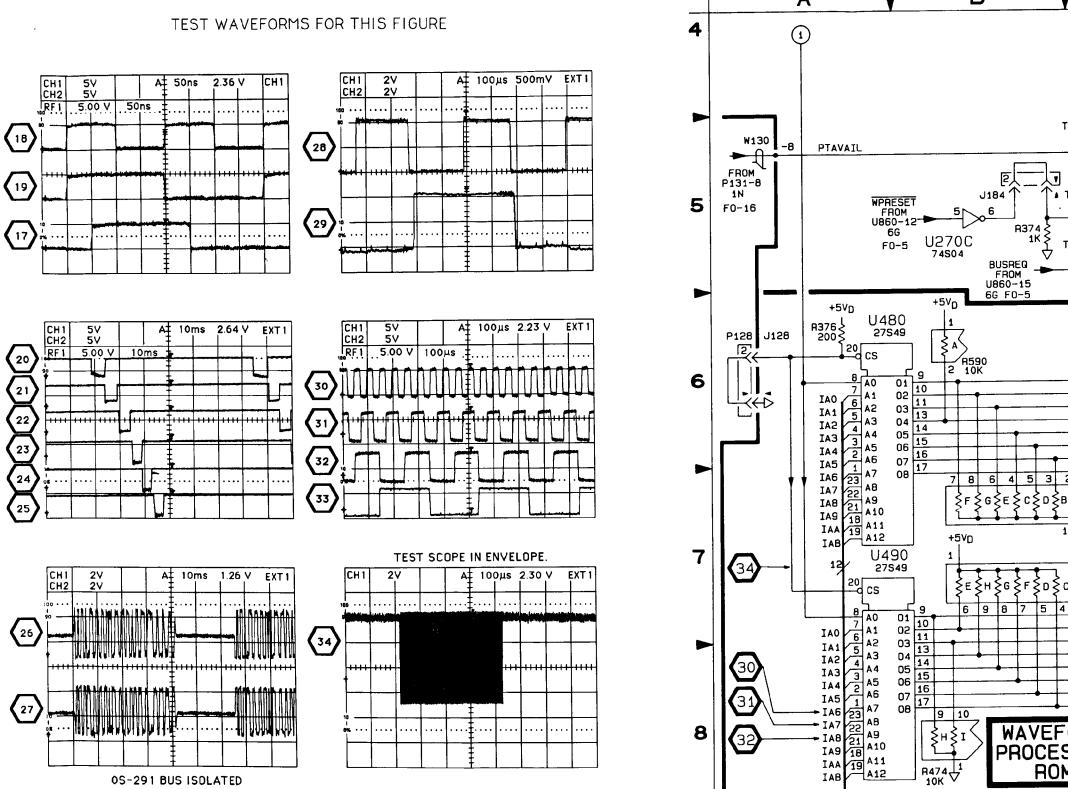

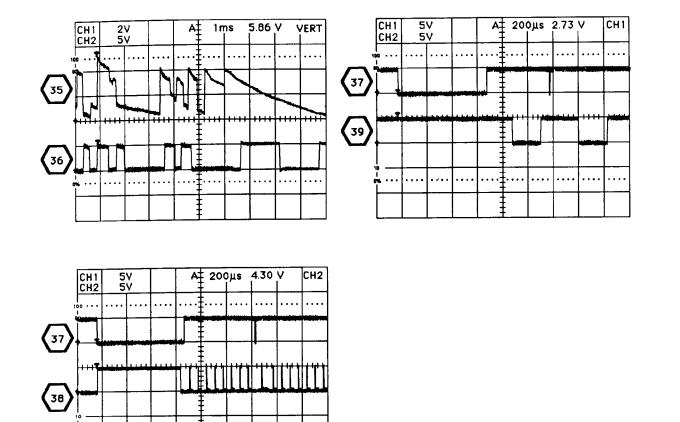

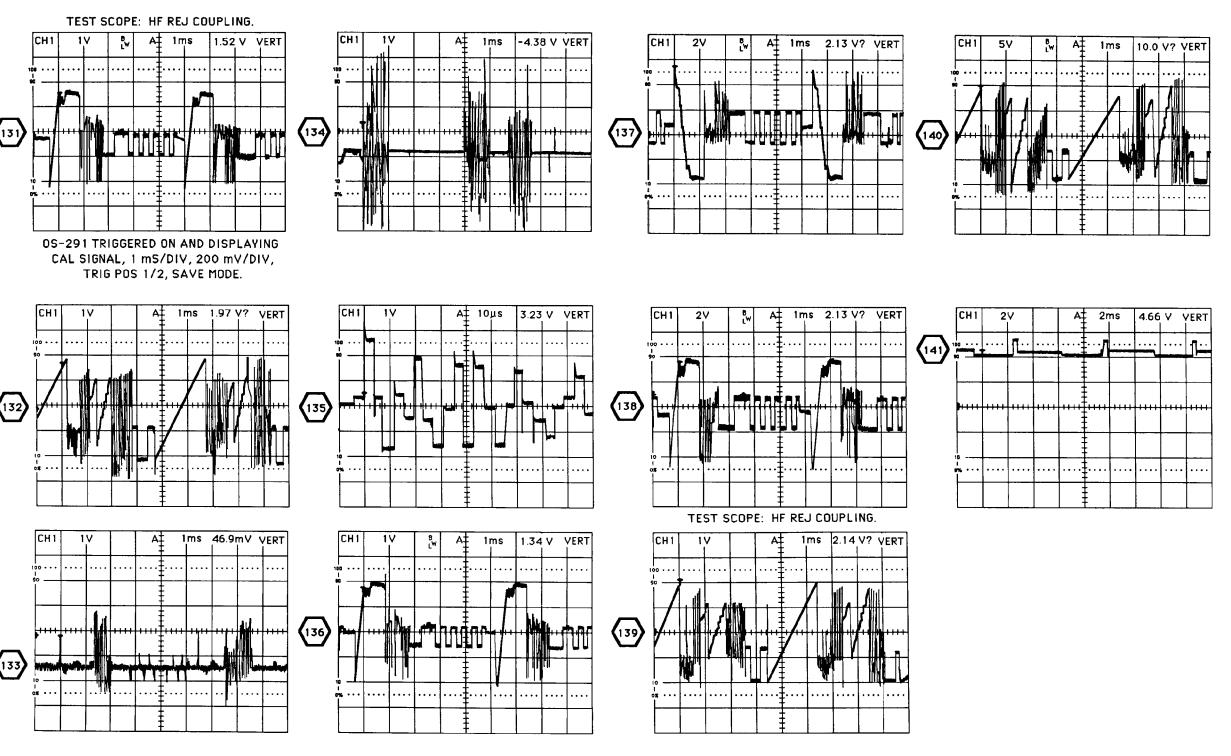

| 6-7    | Mux Test waveforms                                                                          | 6-38 |

| 6-8    | Typical Register test waveforms                                                             | 6-51 |

| 6-9    | Front Panel Microprocessor diagnostics test                                                 | 6-74 |

| 6-10   | System Processor data bit D7 in the Bus isolate mode                                        | 6-95 |

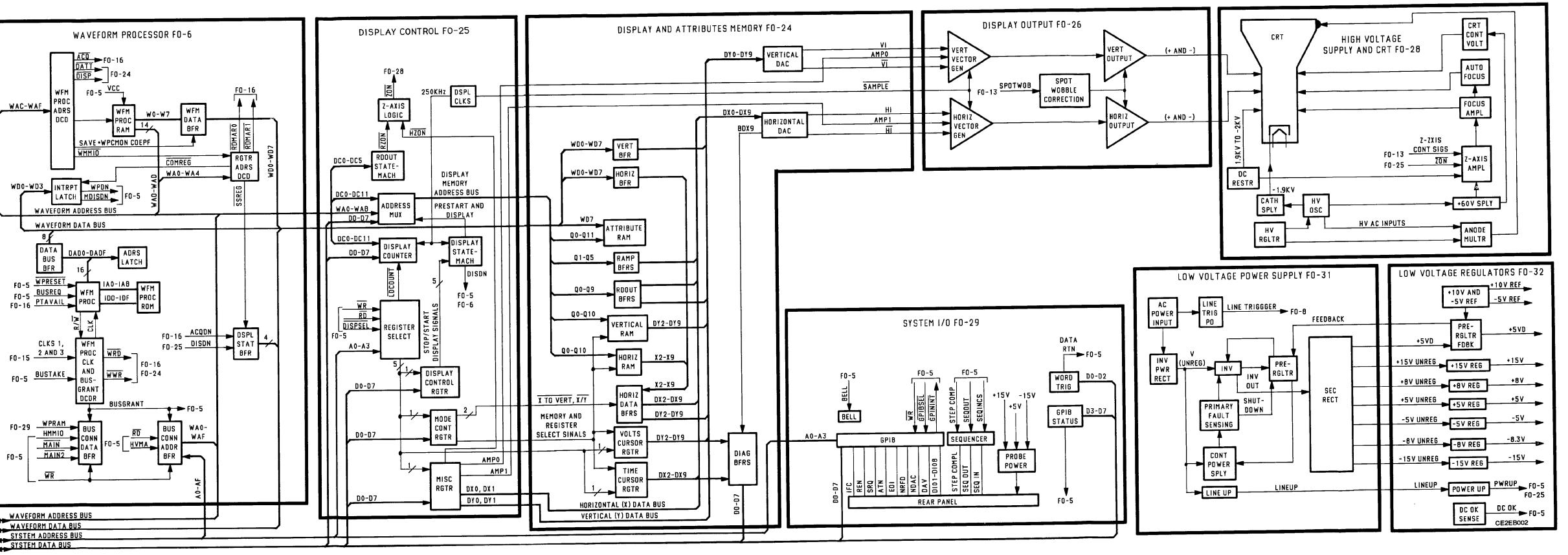

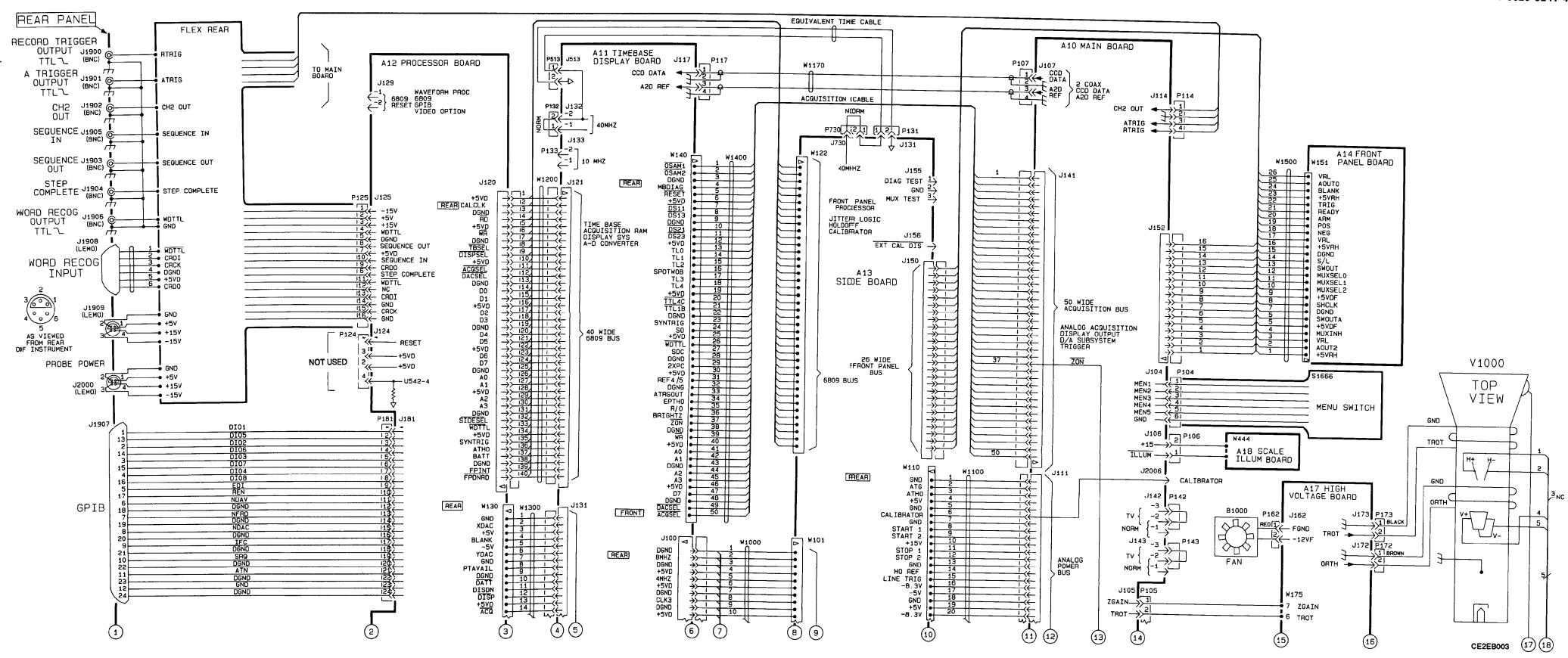

| FO-1   | Block Diagram                                                                               | FP-1 |

| FO-2   | Circuit Board Interconnection Diagram                                                       | FP-5 |

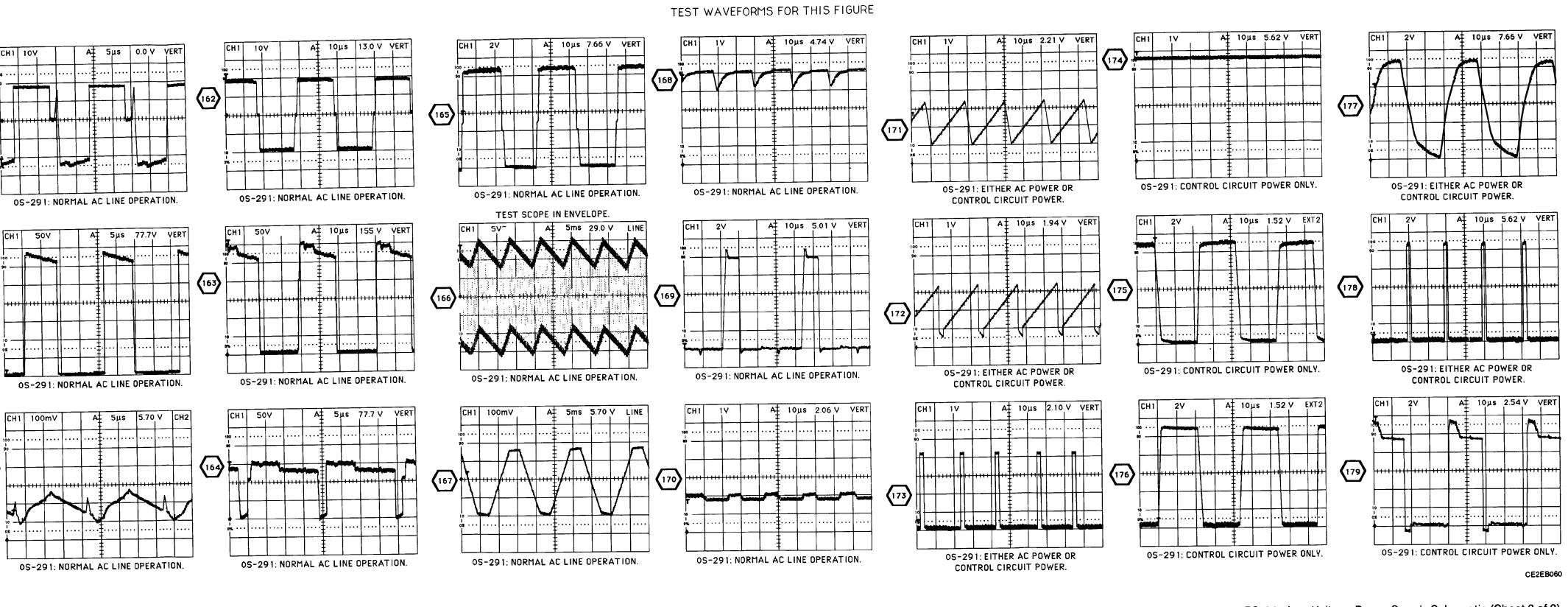

| FO-3   | Chassis Parts, Test Equipment, and Setups for Test Waveforms and Voltage Measurements       | FP-9 |

## LIST OF ILLUSTRATIONS-CONT

| Title                                                                    | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

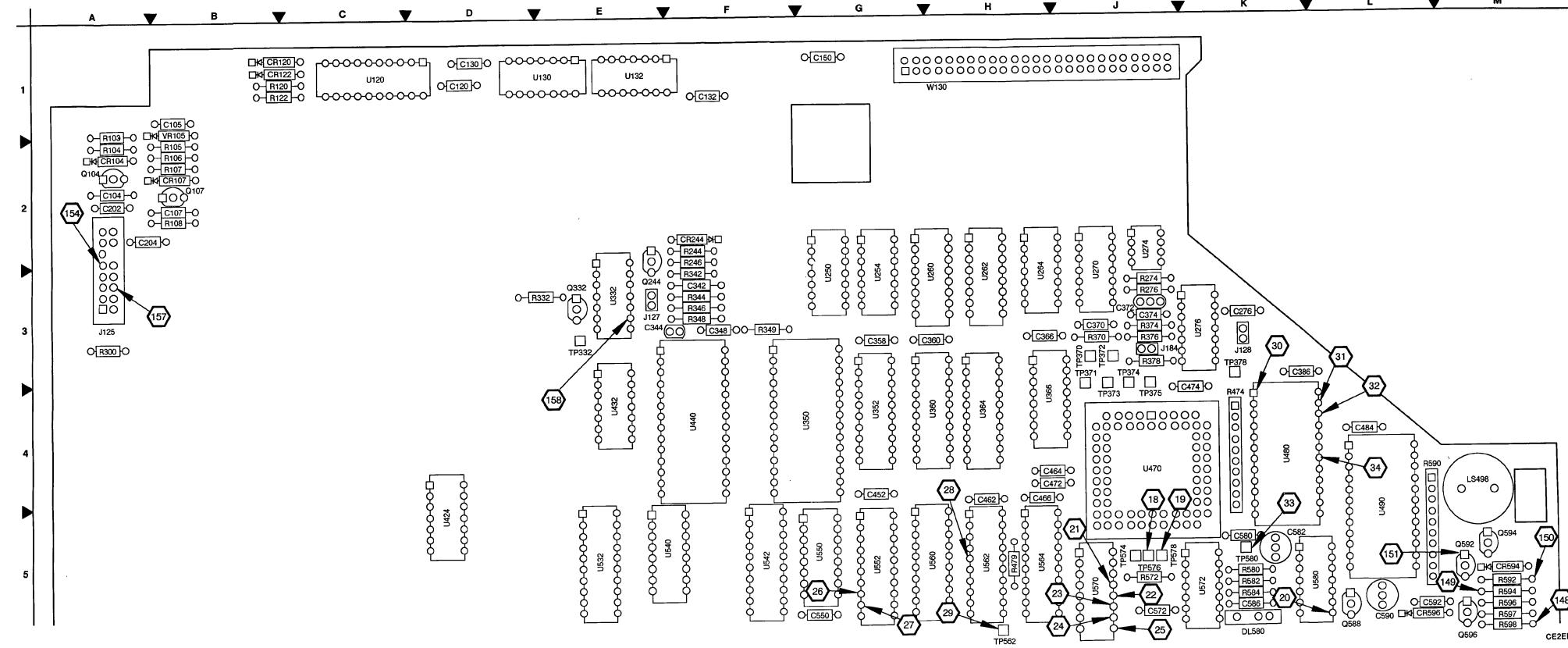

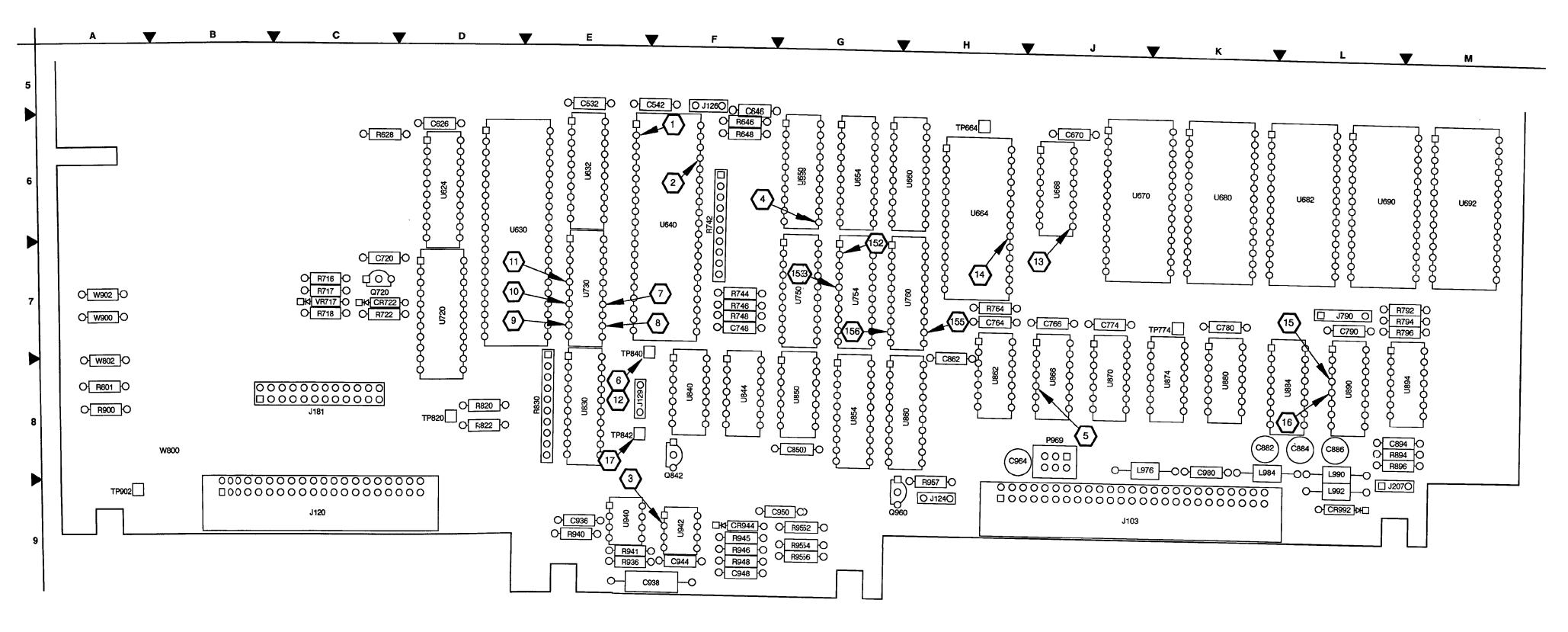

| A12 Processor Board Component Locator                                    | FP-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

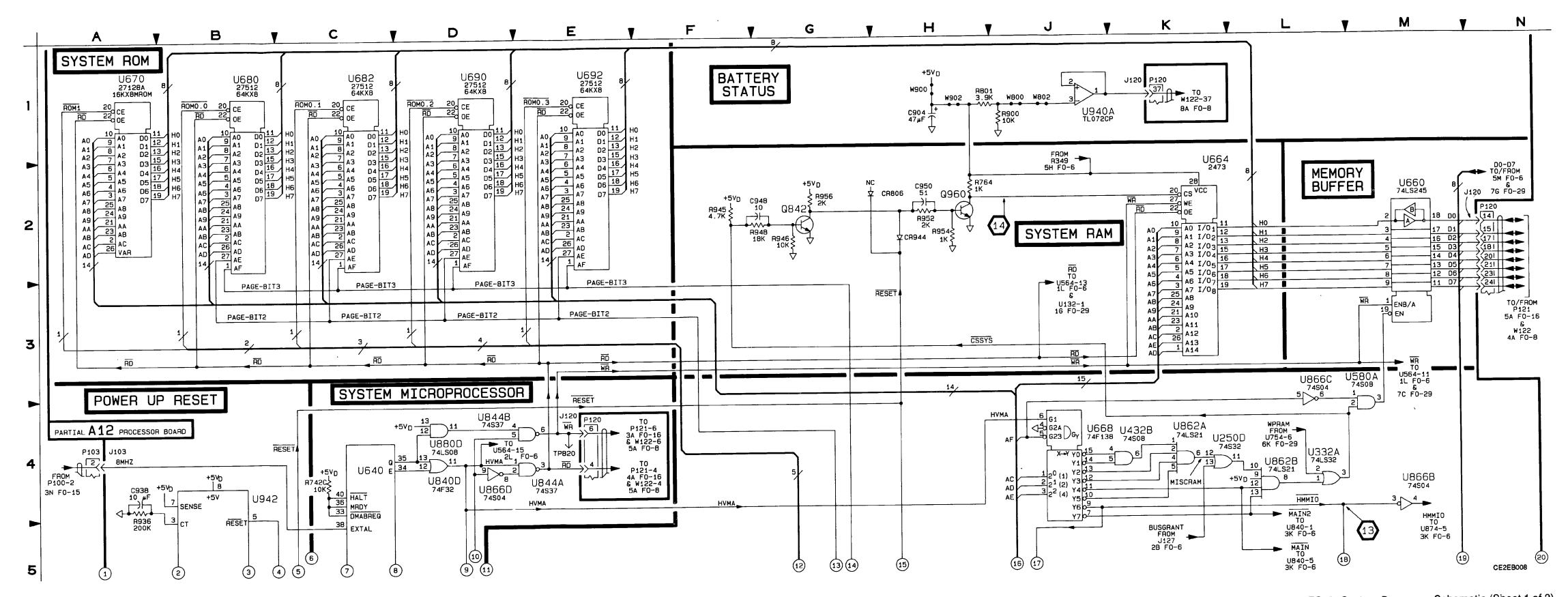

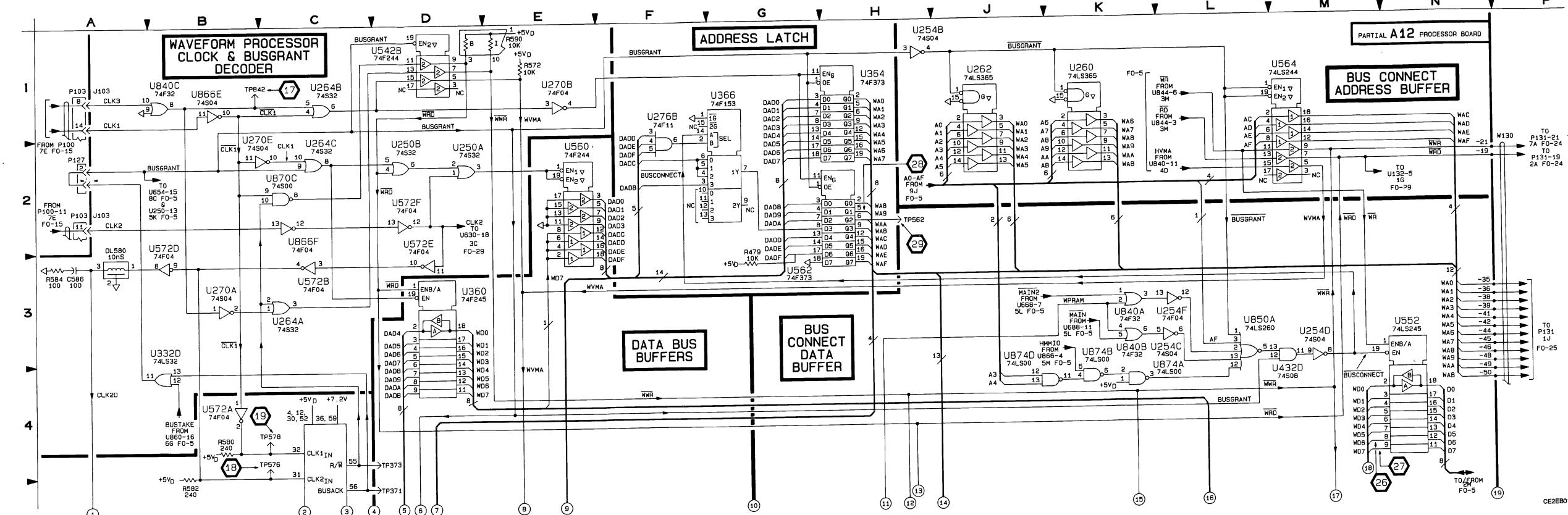

| System Processor Schematic                                               | FP-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

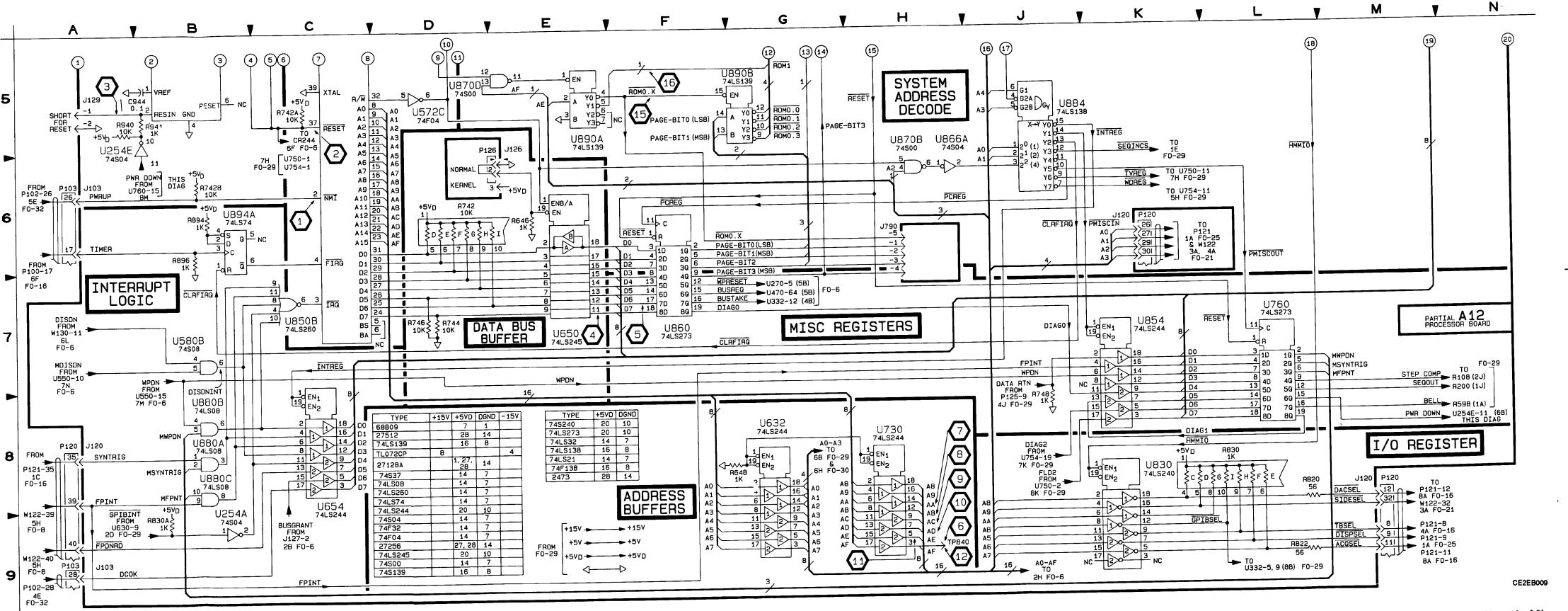

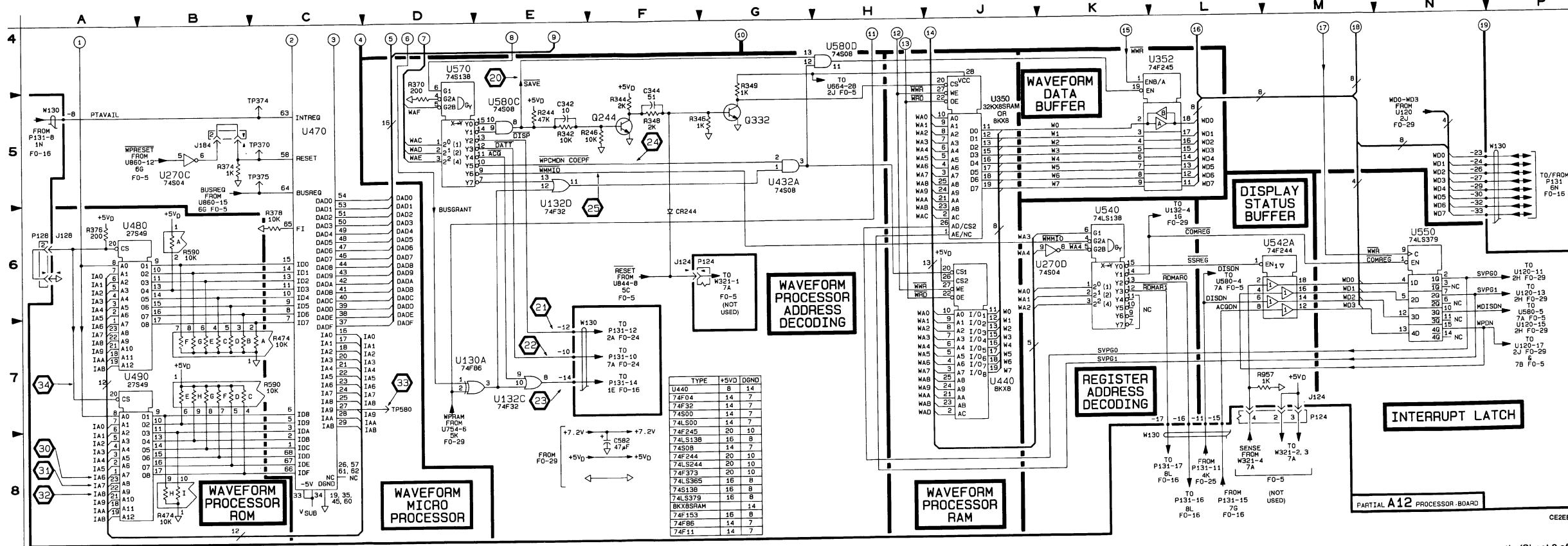

| Waveform Processor Schematic                                             | FP-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

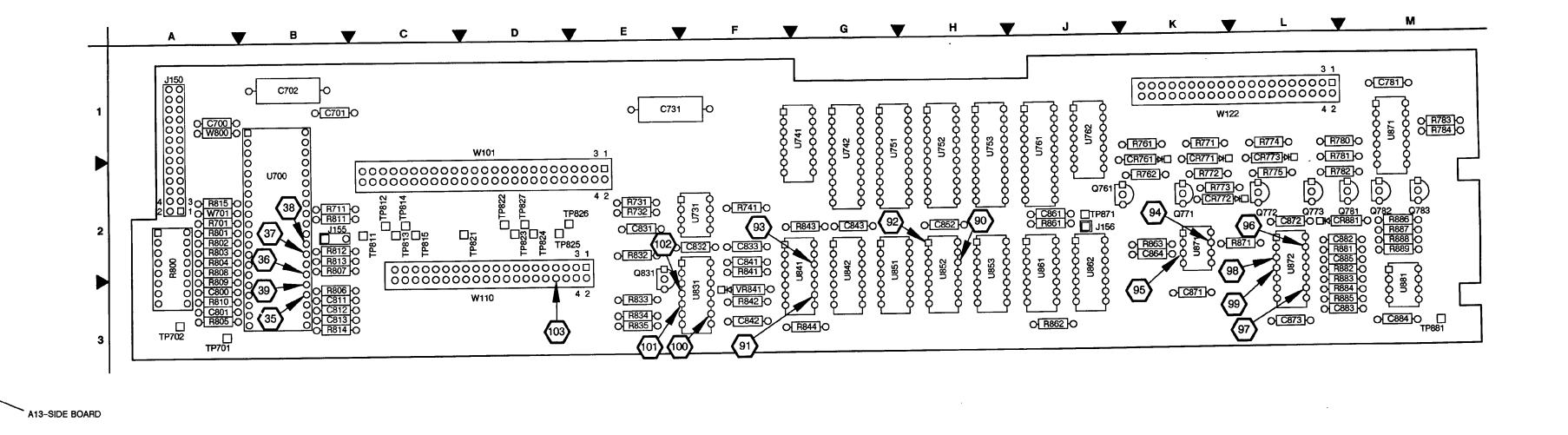

| A13 Side Board Component Locator                                         | FP-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

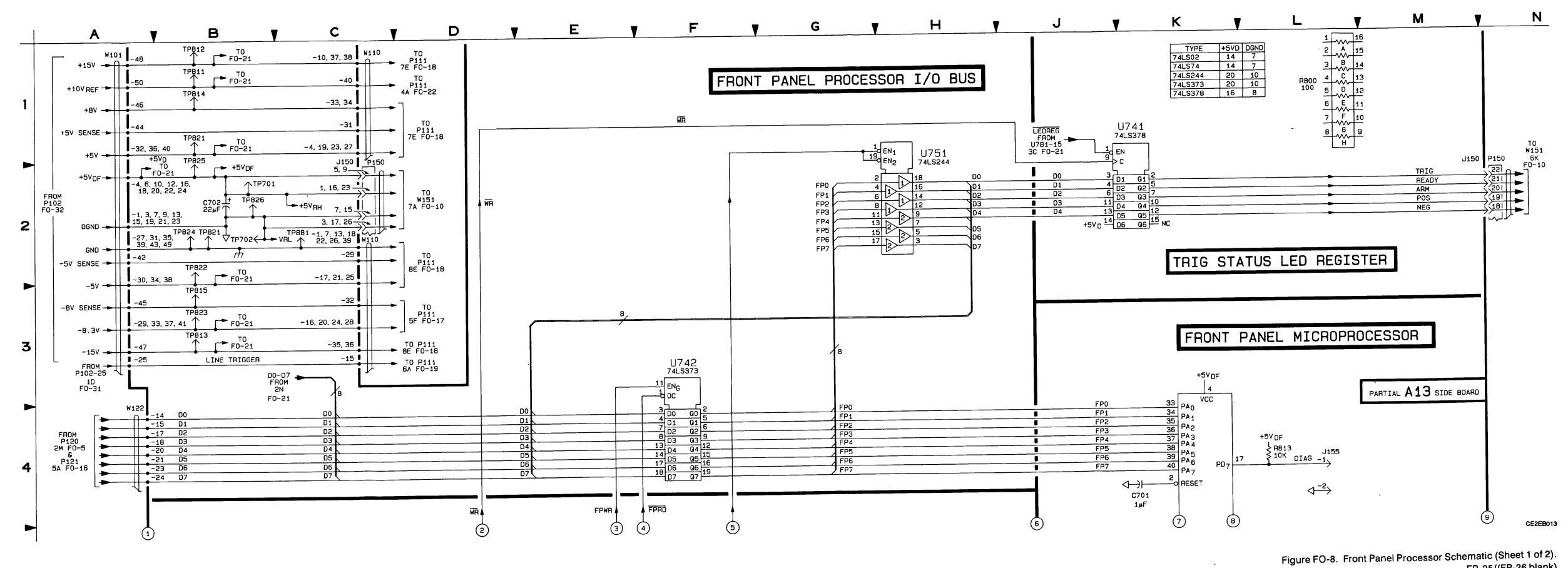

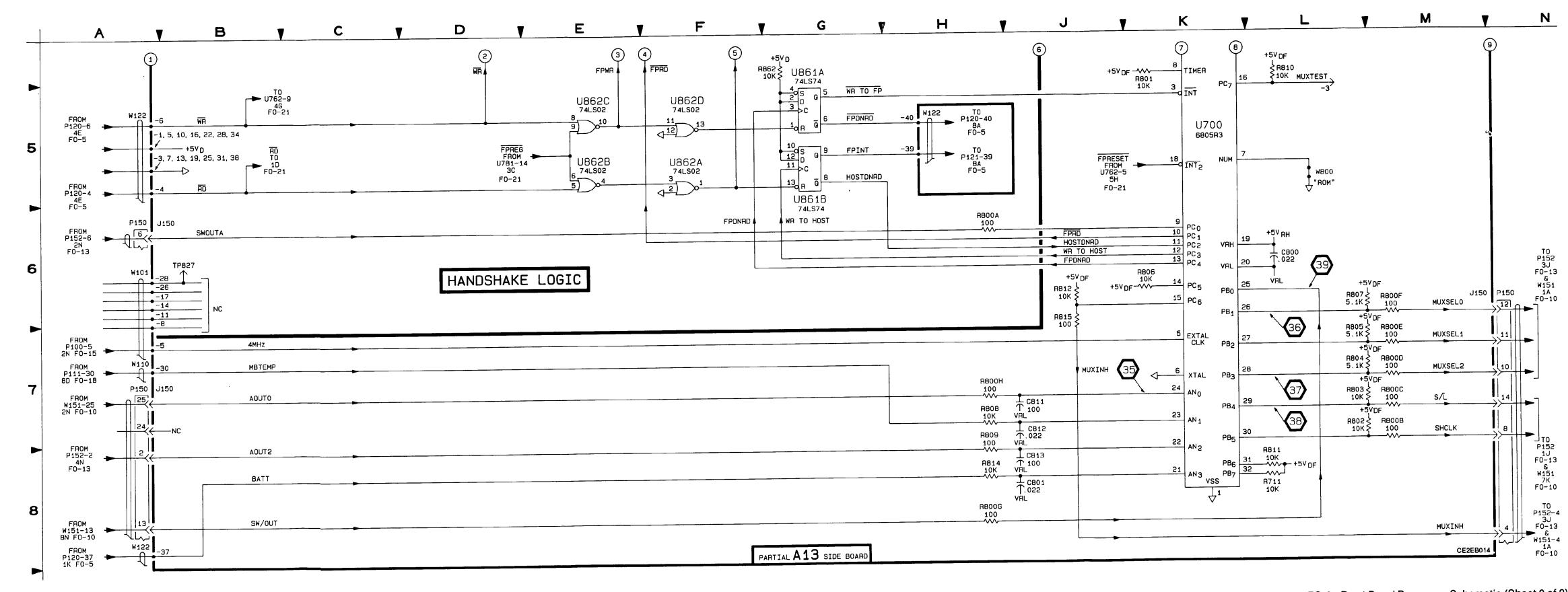

| Front Panel Processor Schematic                                          | FP-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

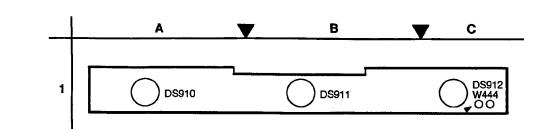

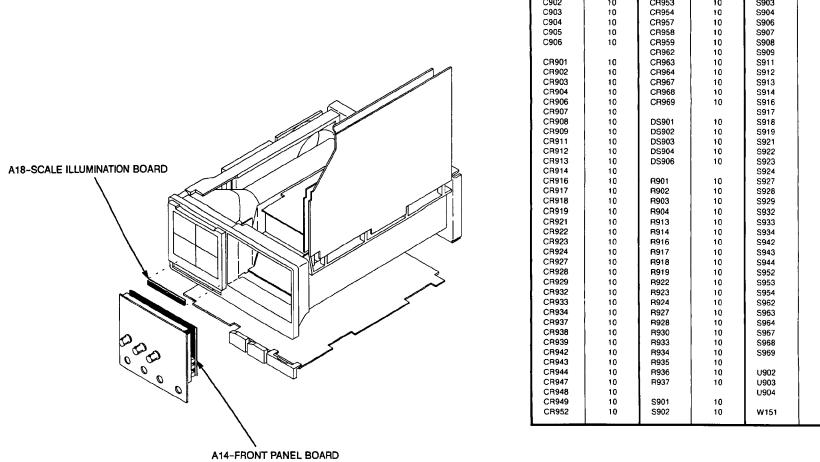

| A14 Front Panel Board and A18 Scale Illumination Board Component Locator | FP-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

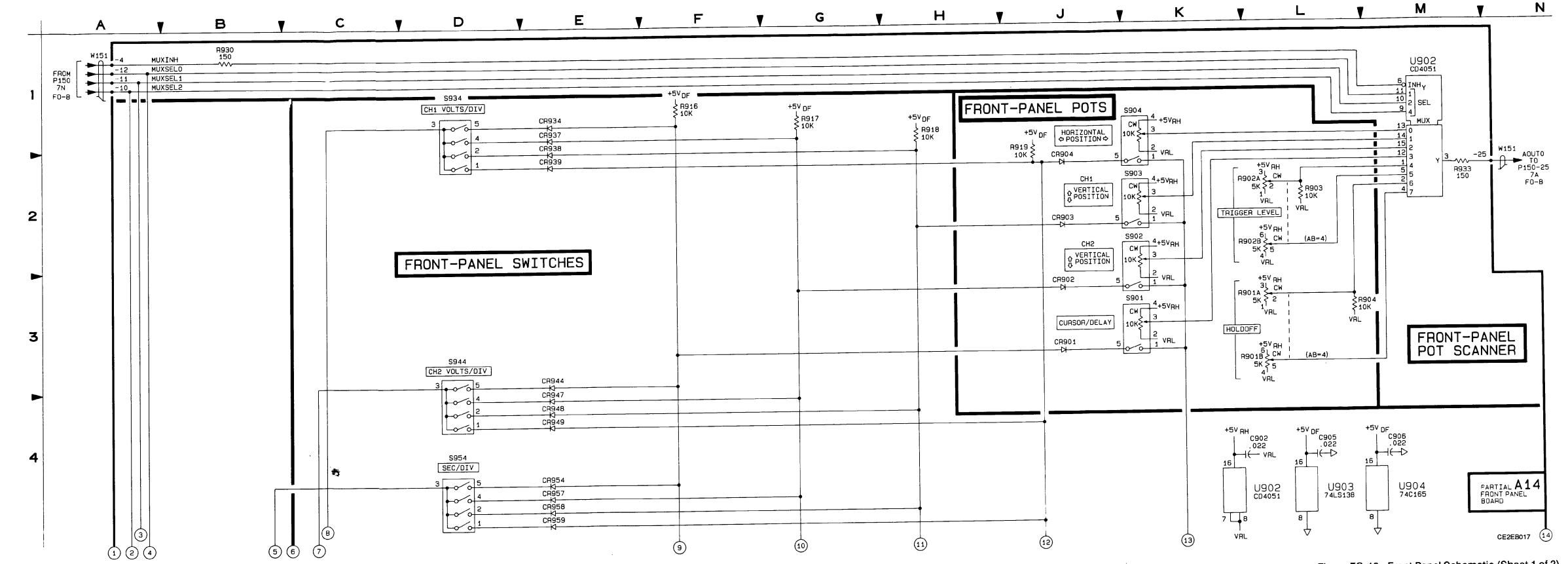

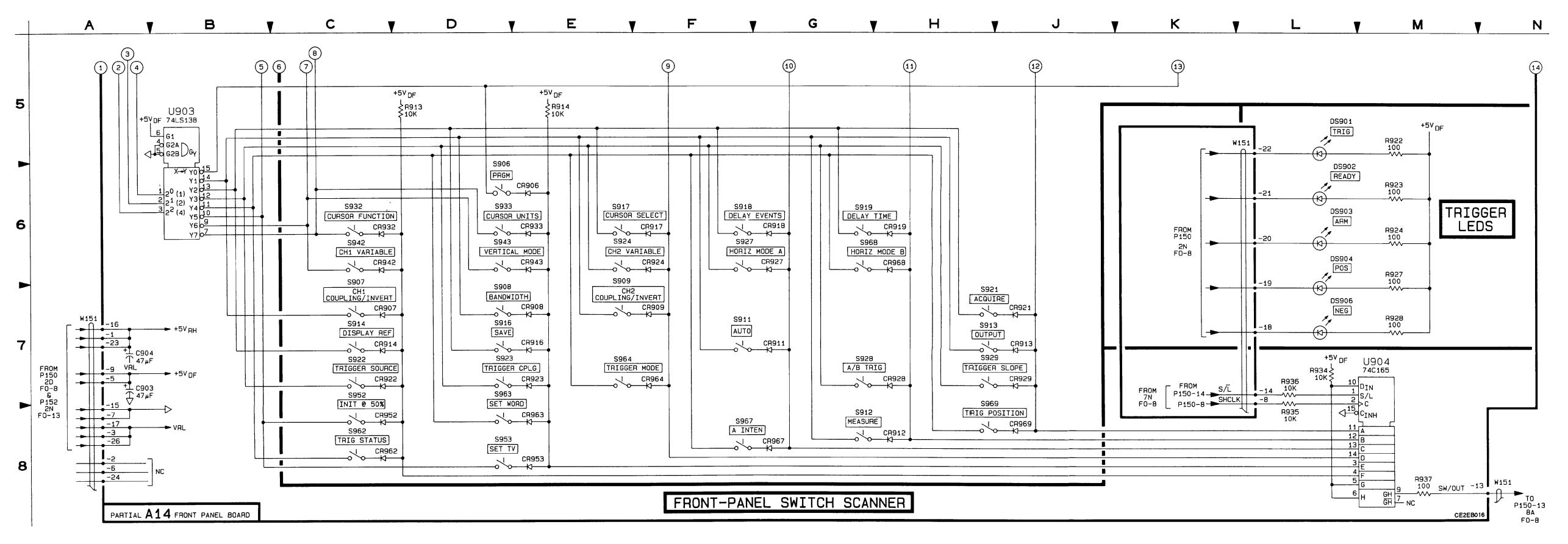

| Front Panel Schematic                                                    | FP-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

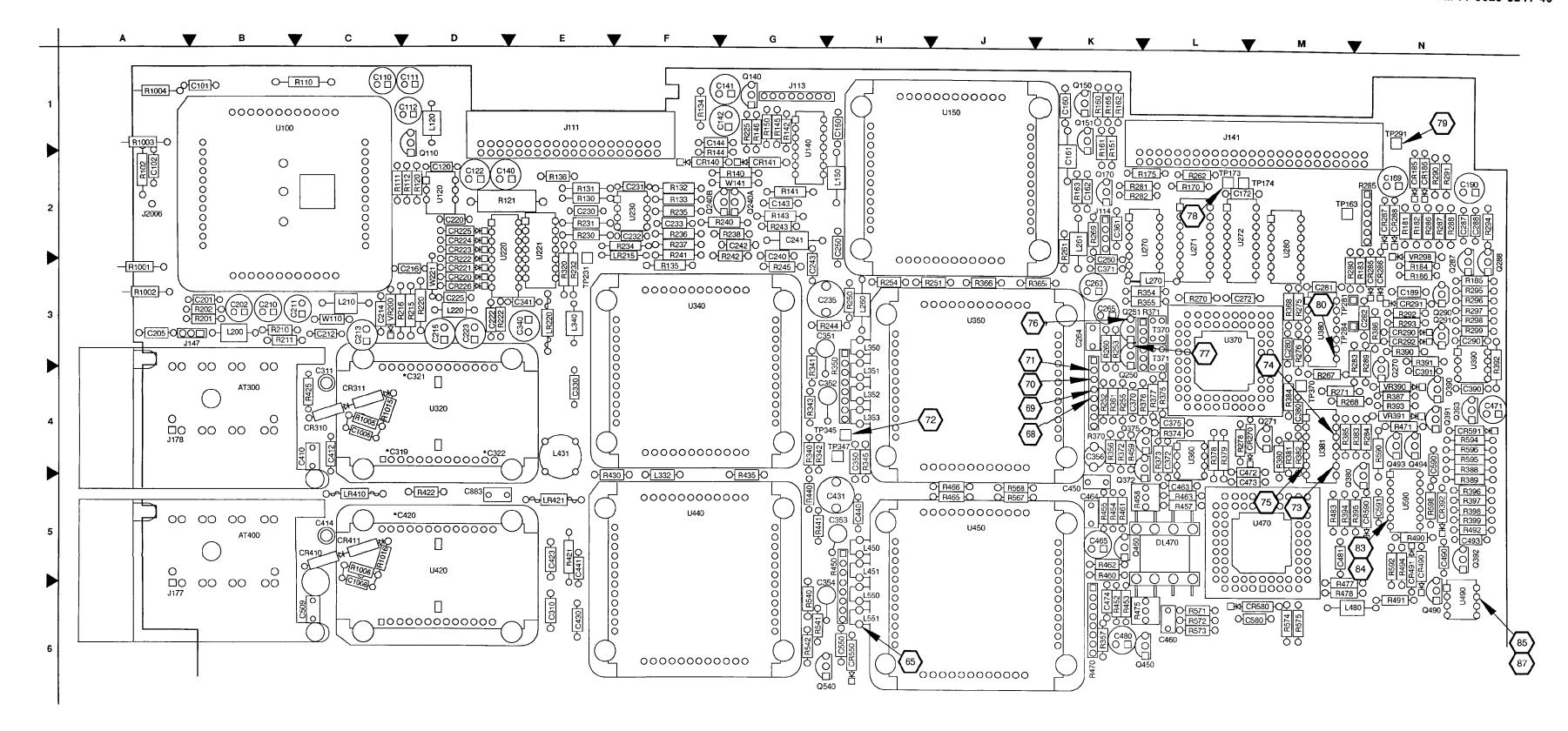

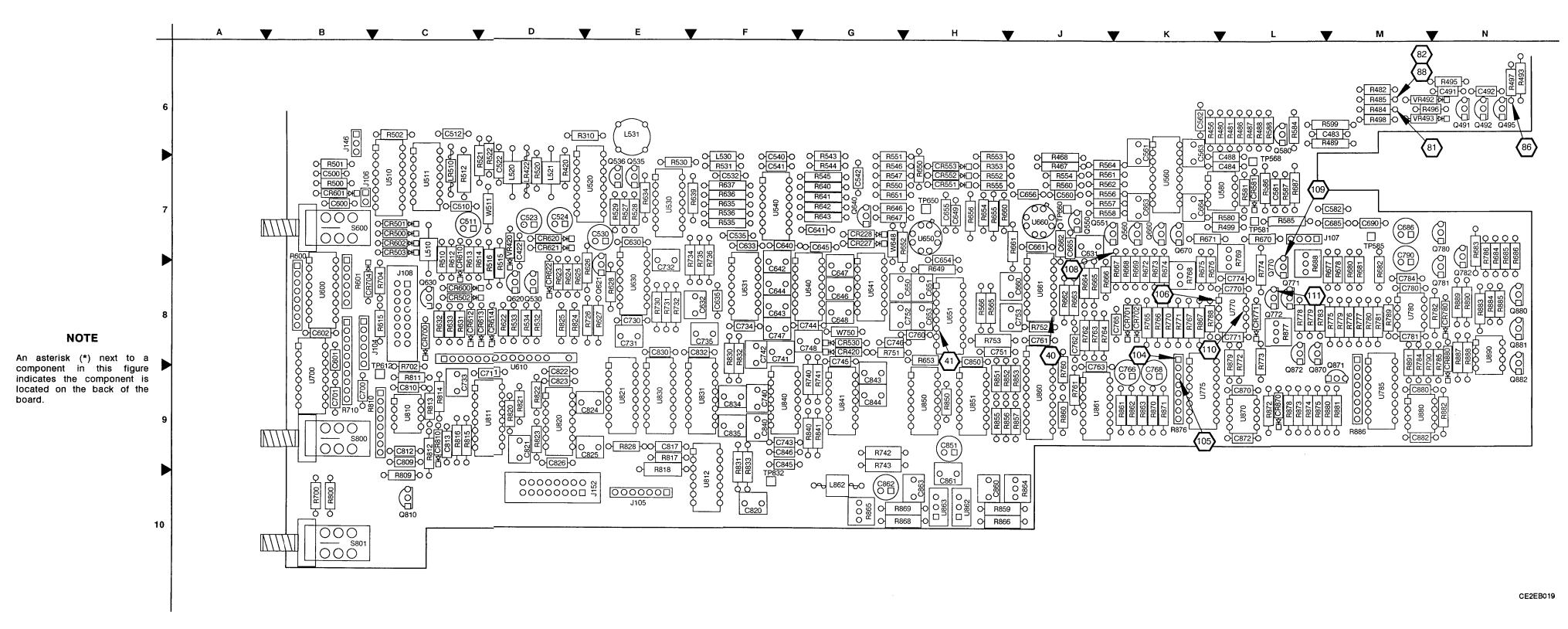

| A10 Main Board Component Locator                                         | FP-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

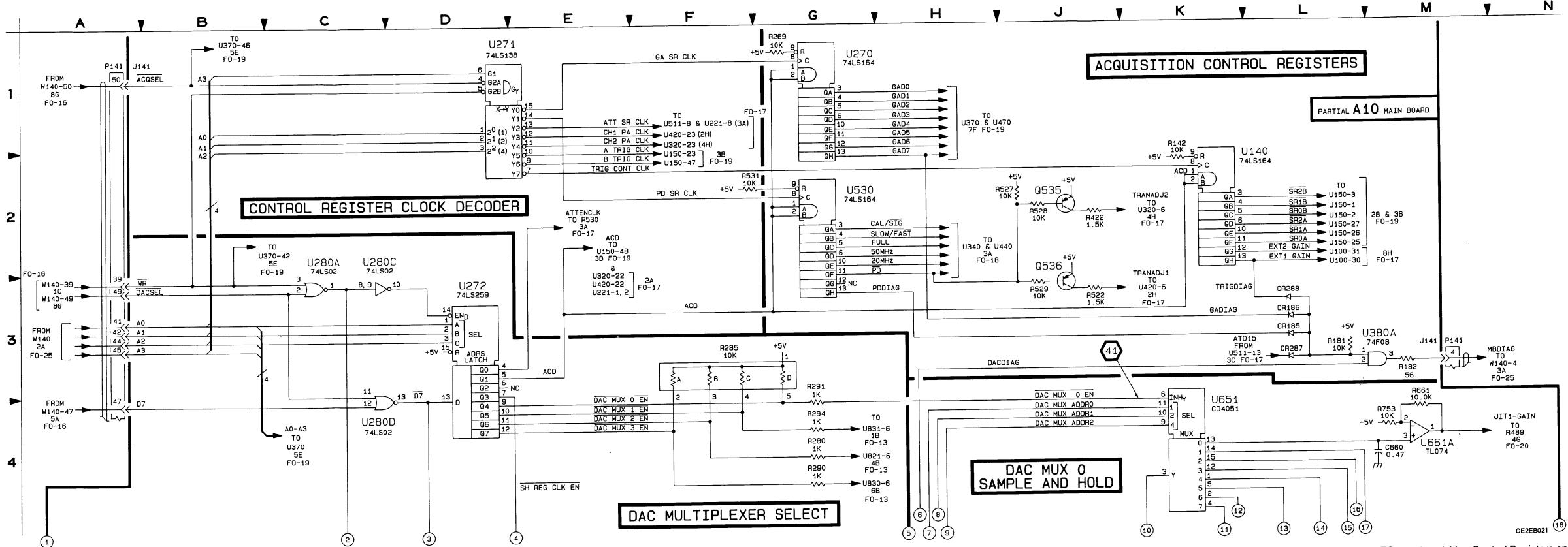

| Acquisition Control Registers and System DAC Schematic                   | FP-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

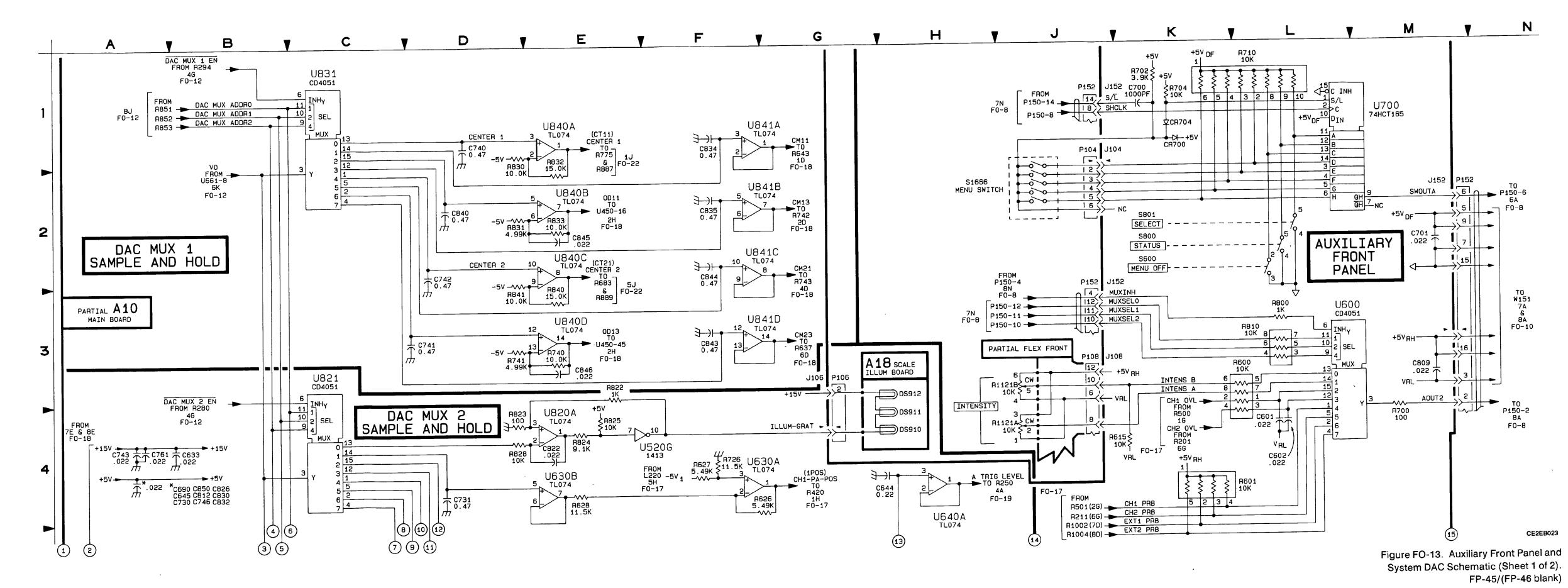

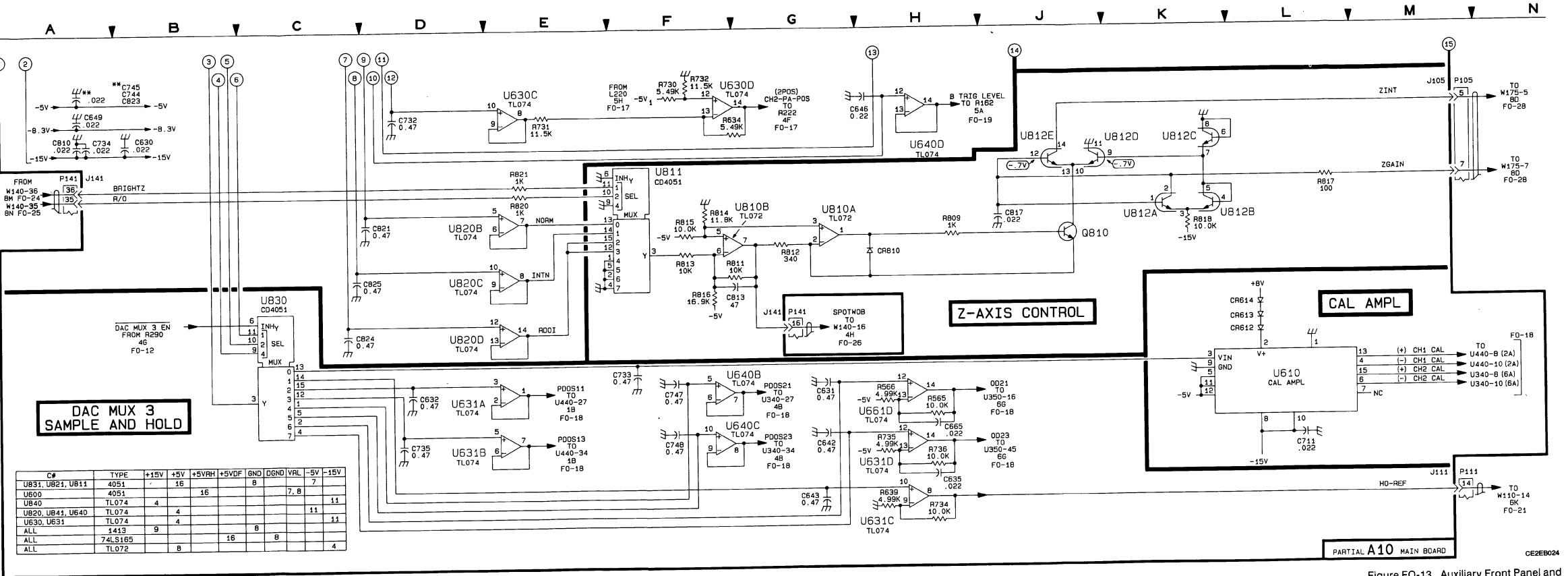

| Auxiliary Front Panel and System DAC Schematic                           | FP-45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

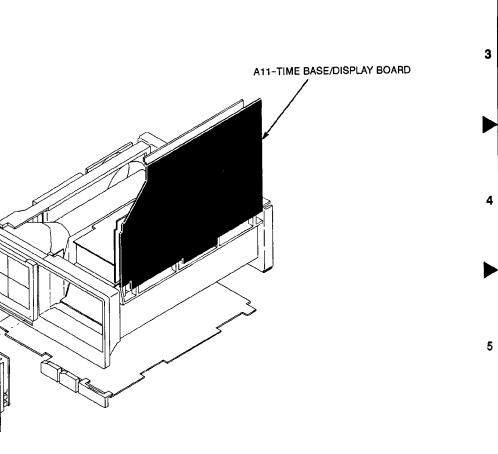

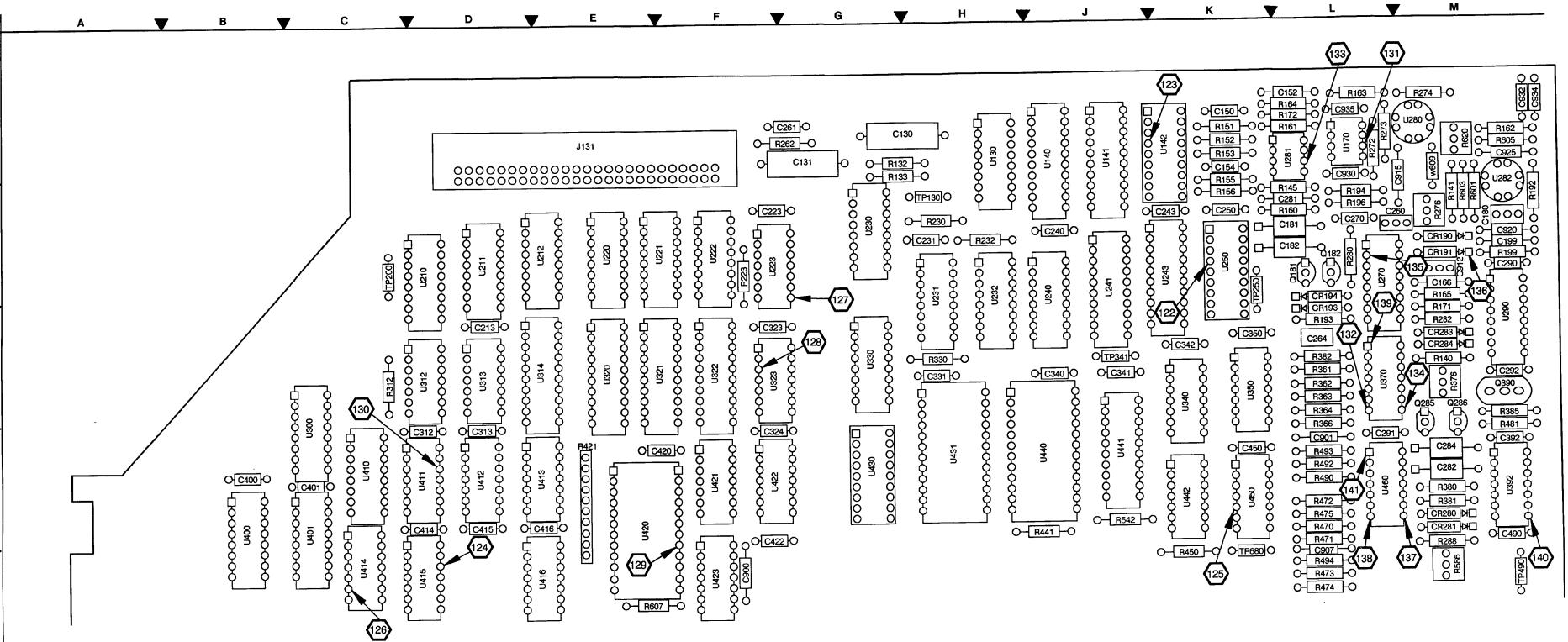

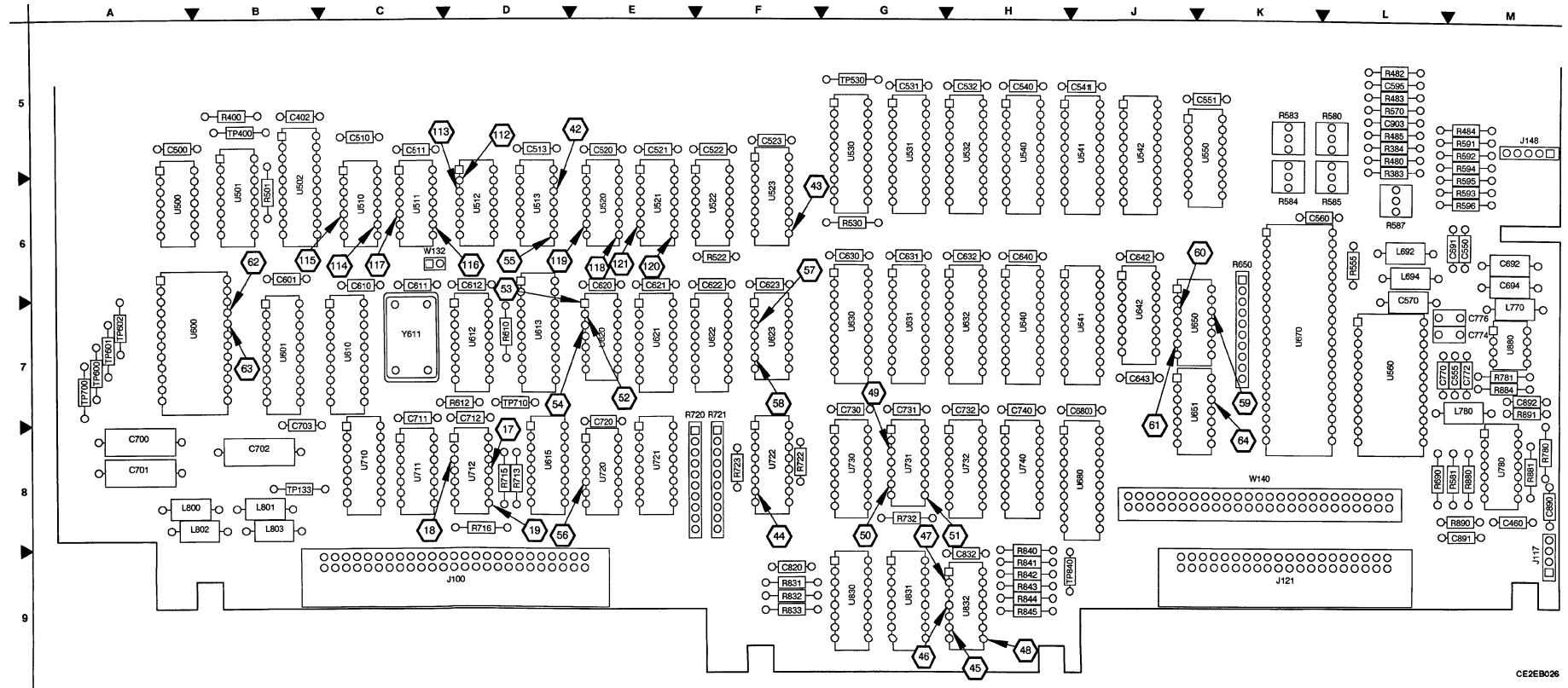

| All Time Base/Display Board Component Locator                            | FP-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

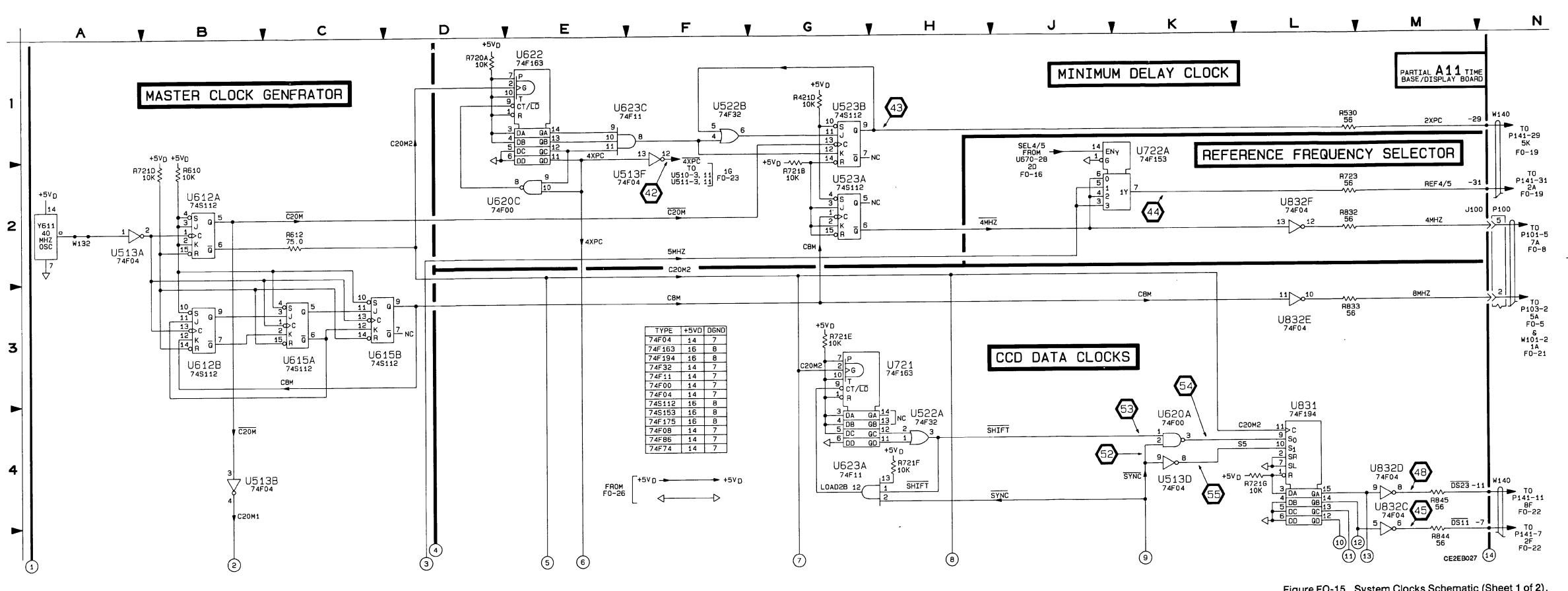

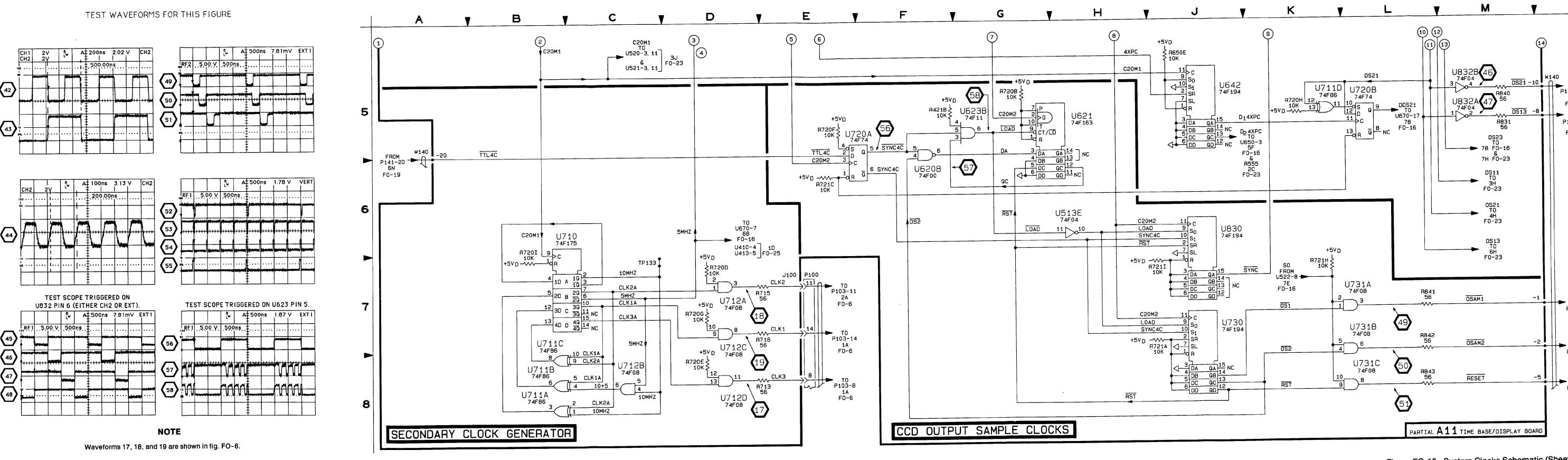

| System Clocks Schematic                                                  | FP-53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

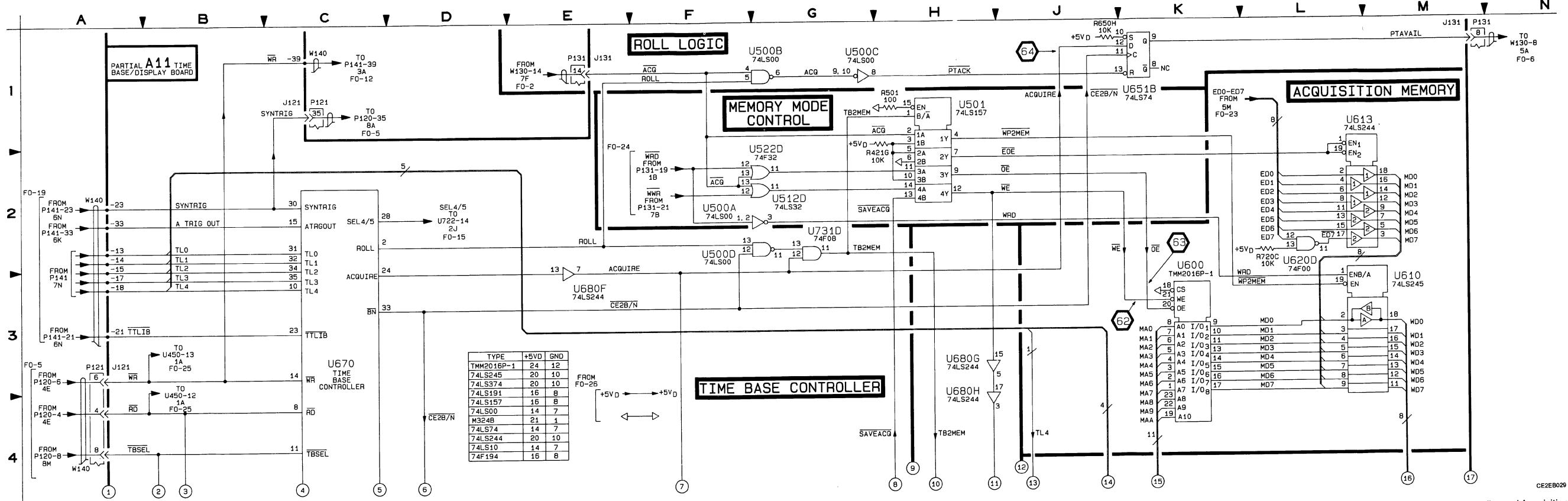

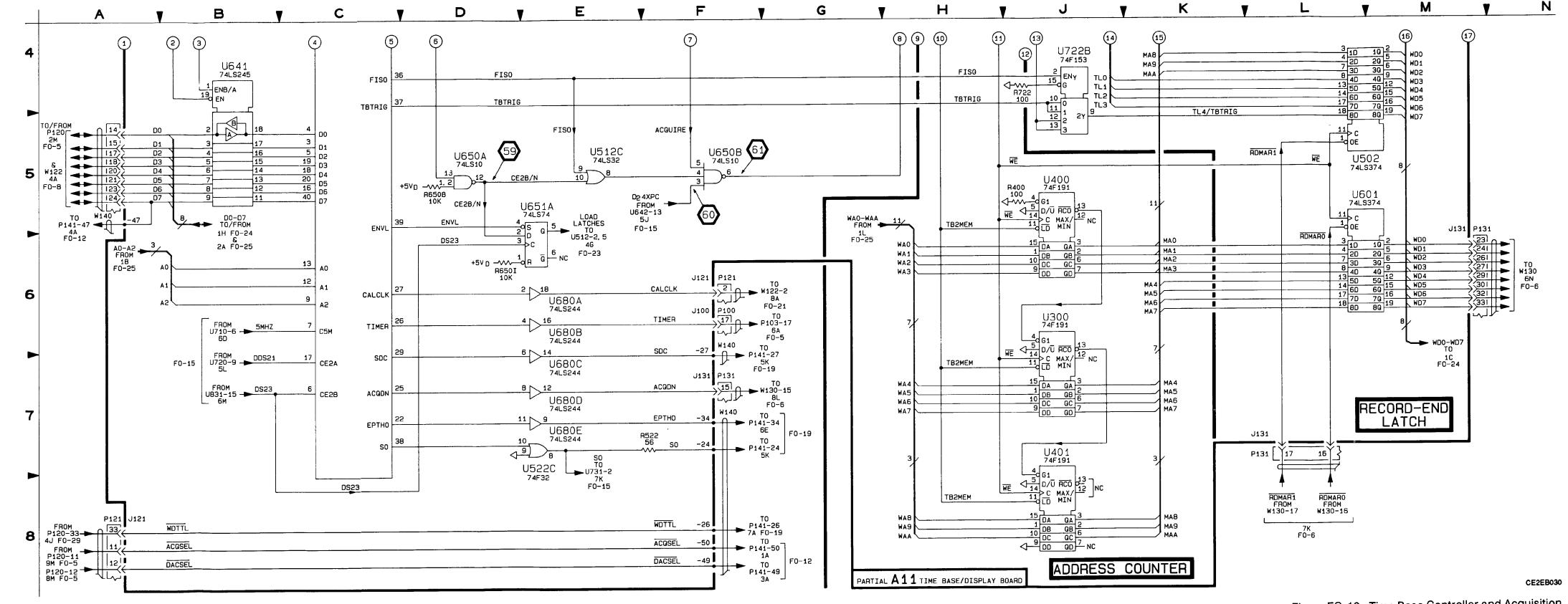

| Time Base Controller and Acquisition Memory Schematic                    | FP-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

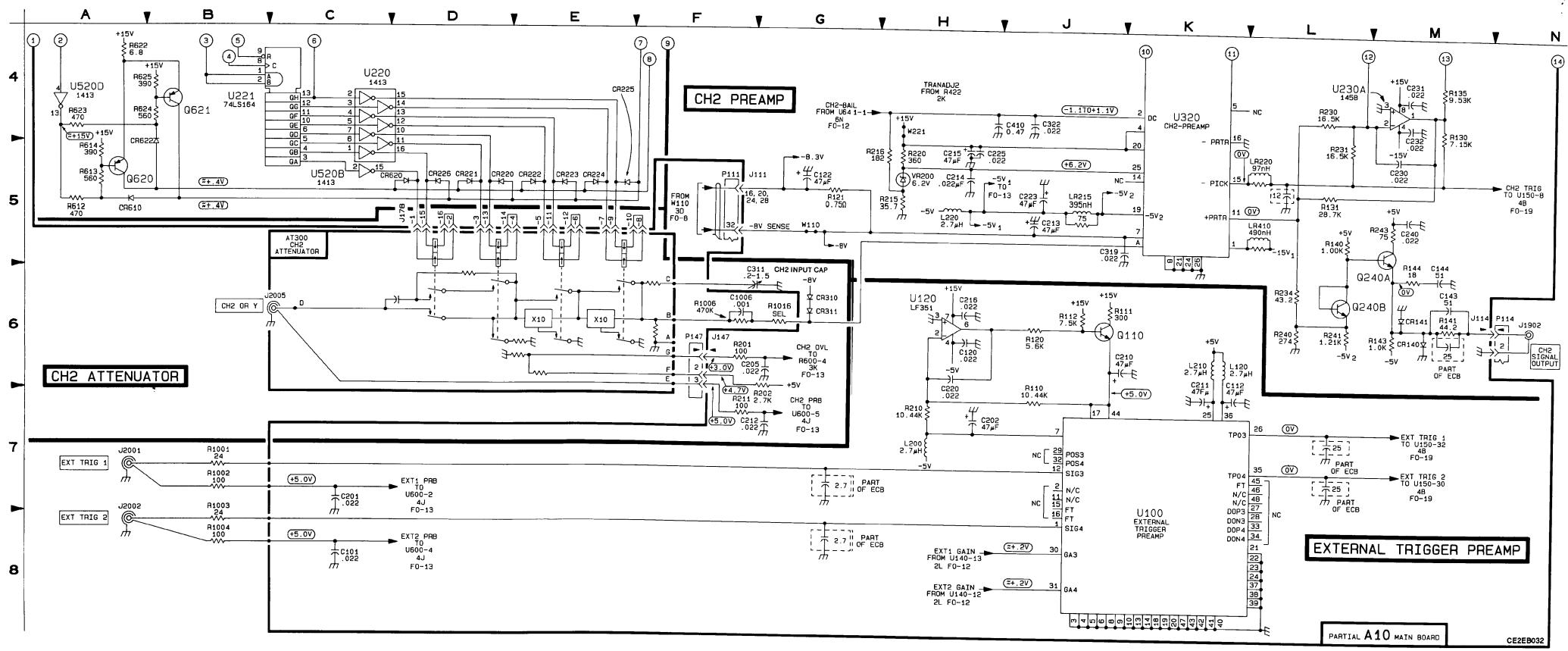

| Attenuators and Preamps Schematic                                        | FP-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

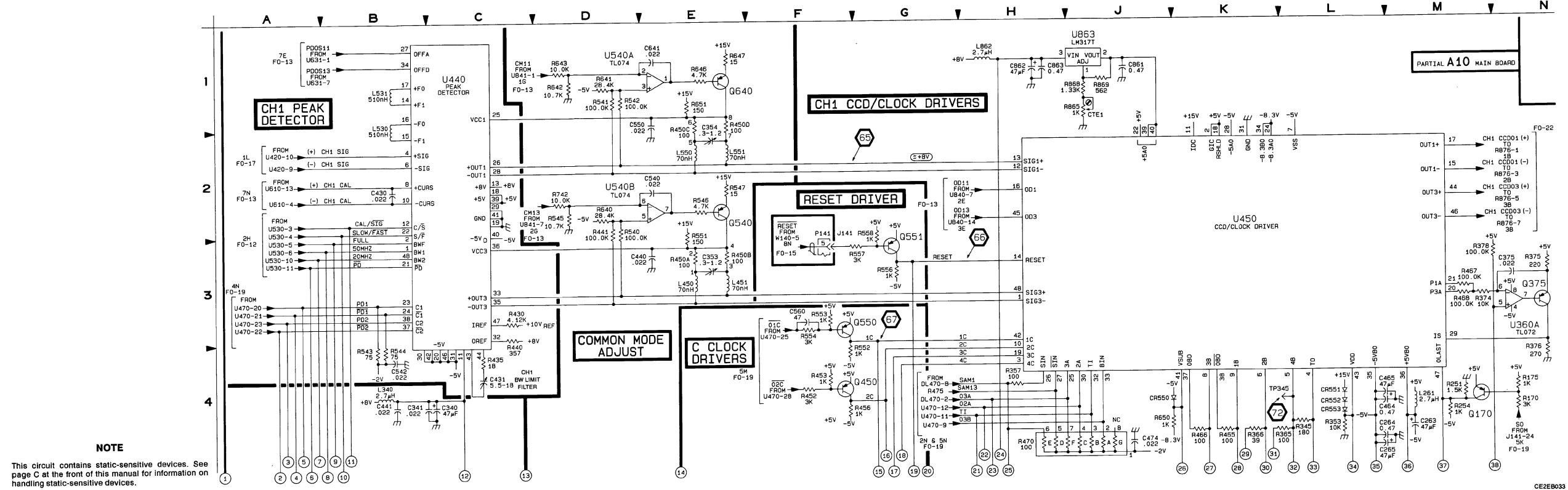

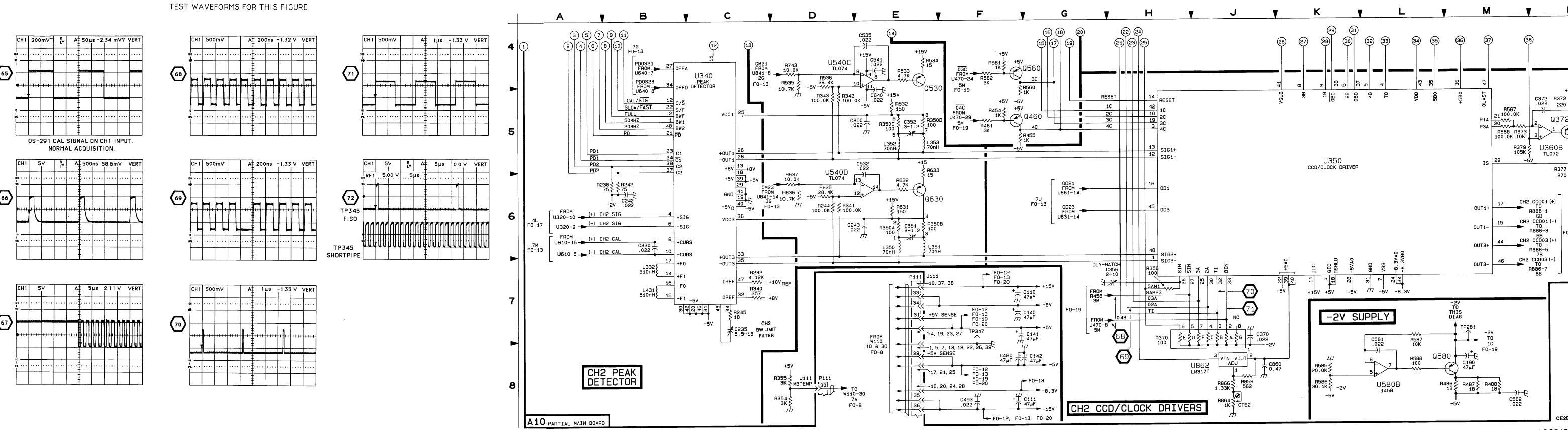

| Peak Detectors and CCD/Clock Drivers Schematic                           | FP-65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

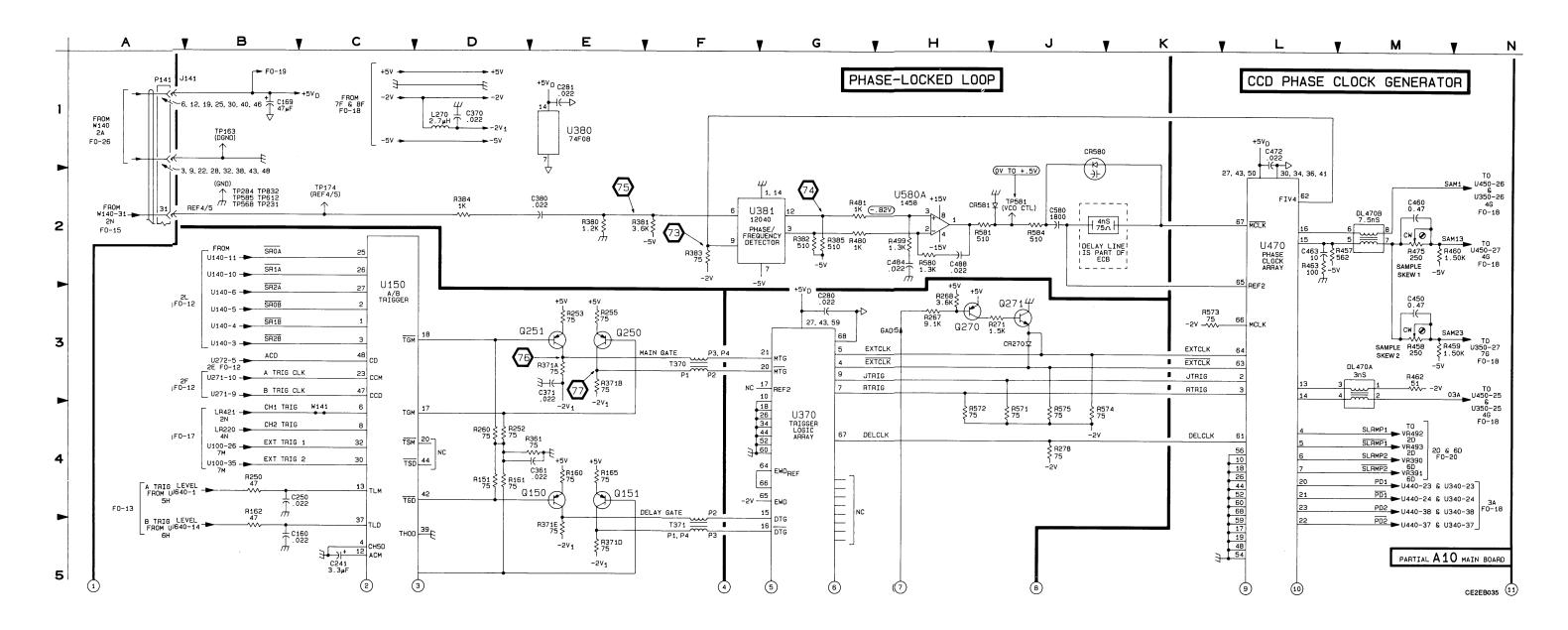

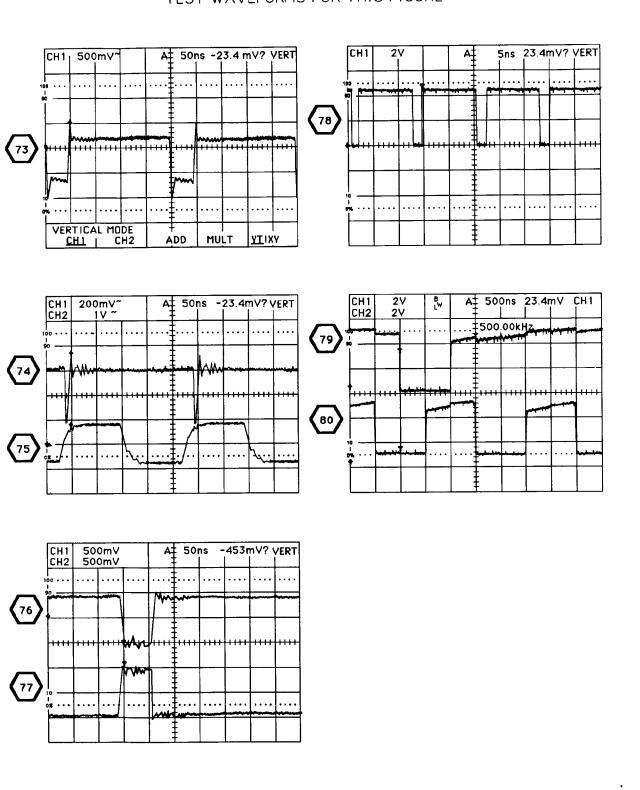

| Triggers and Phase Clocks Schematic                                      | FP-69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

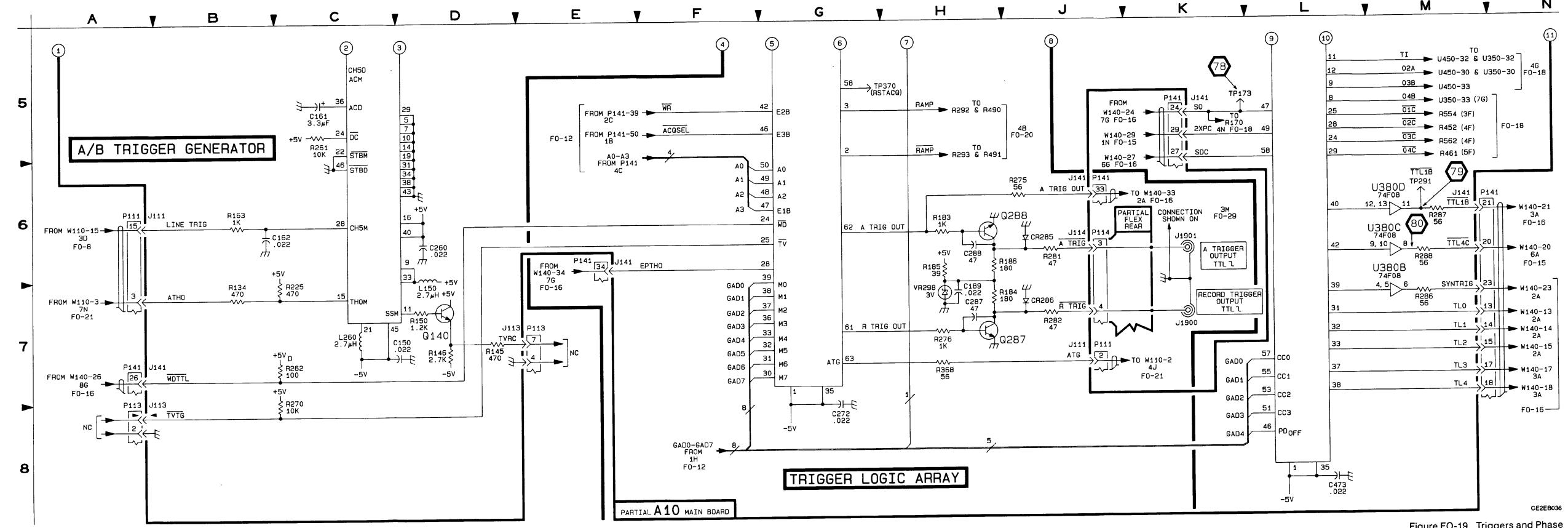

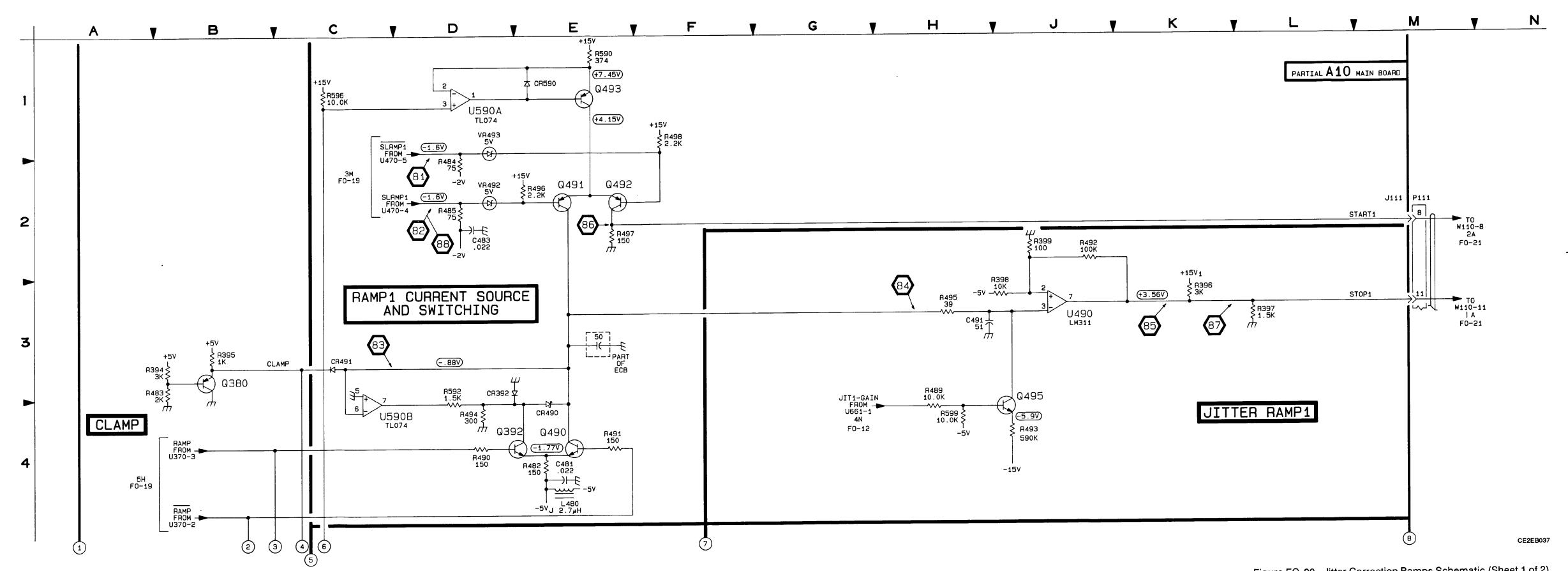

| Jitter Correction Ramps Schematic                                        | FP-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

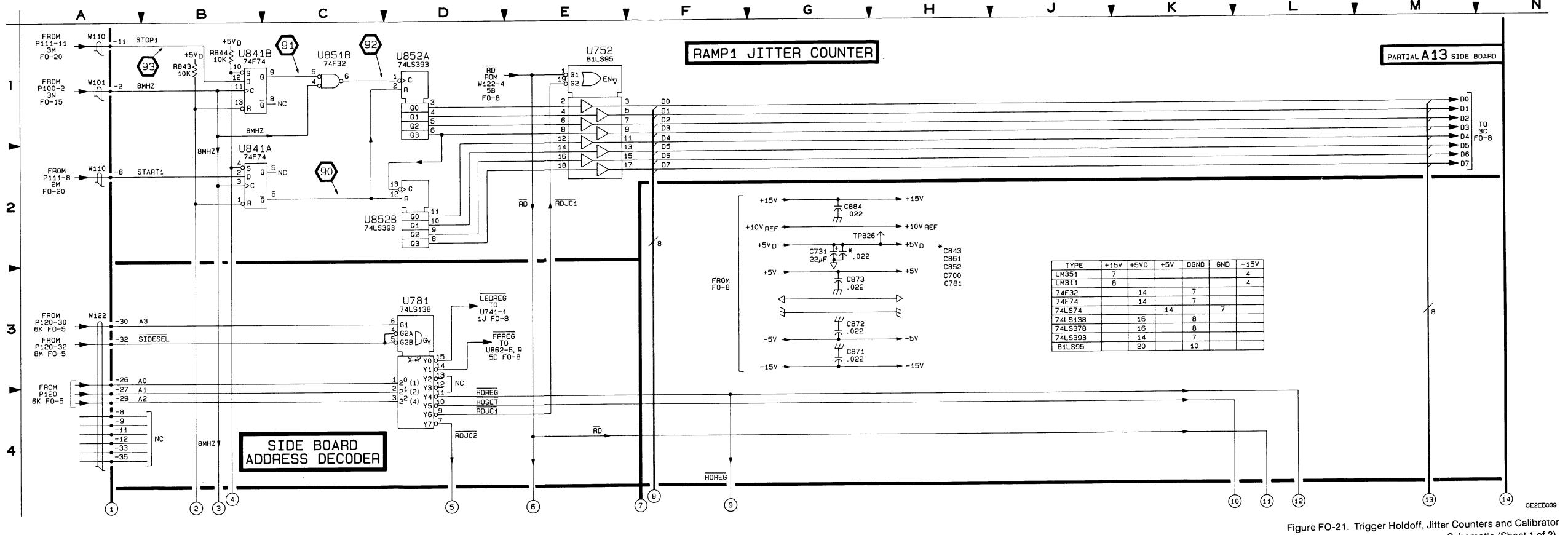

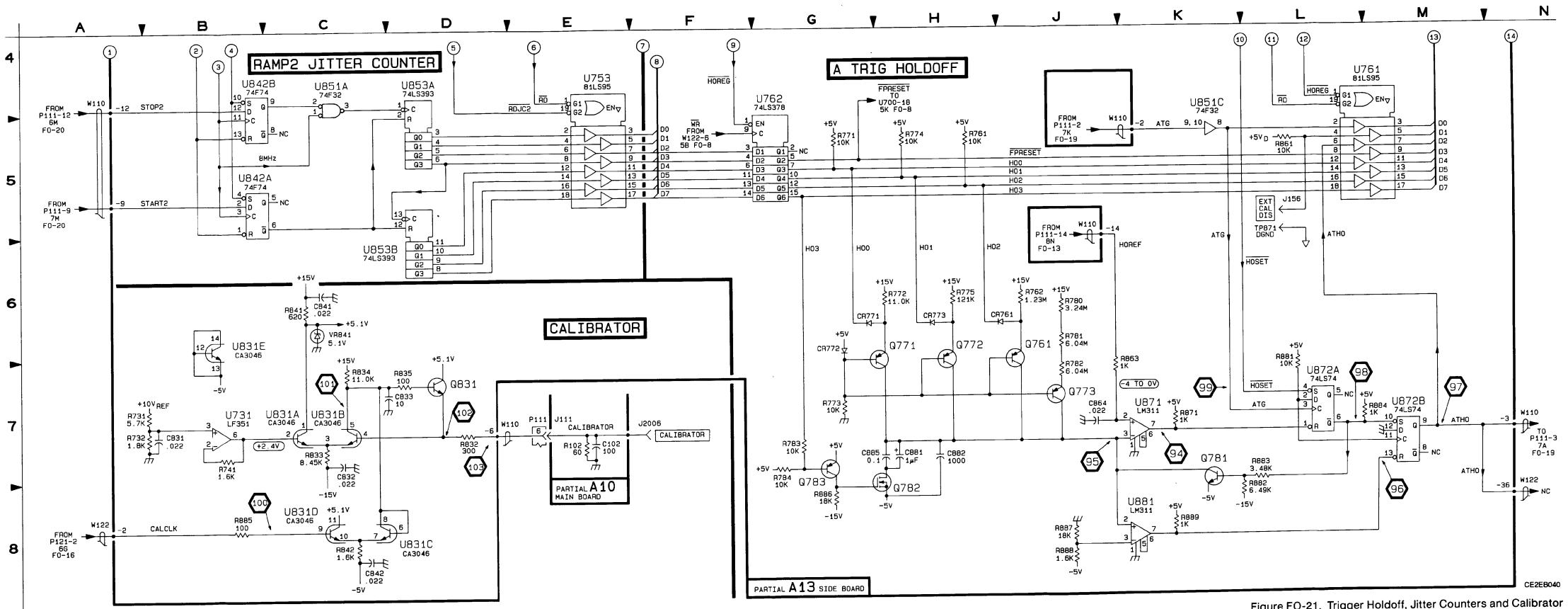

| Trigger Holdoff, Jitter Counters and Calibrator Schematic                | FP-77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

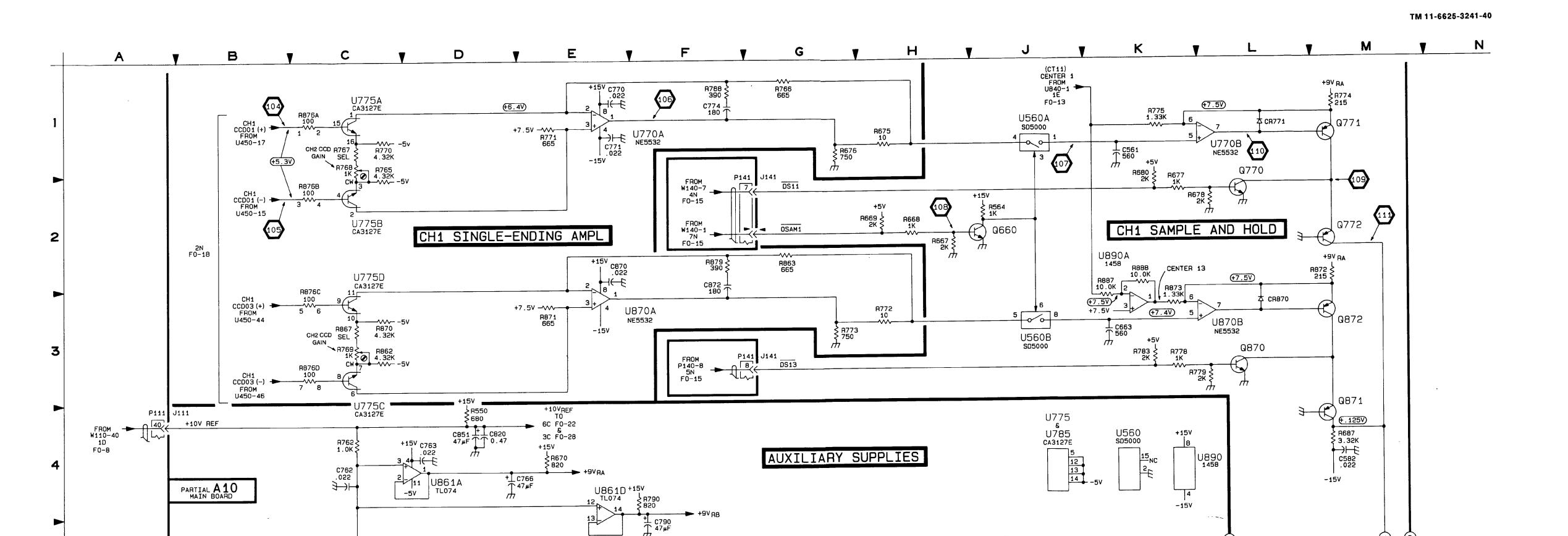

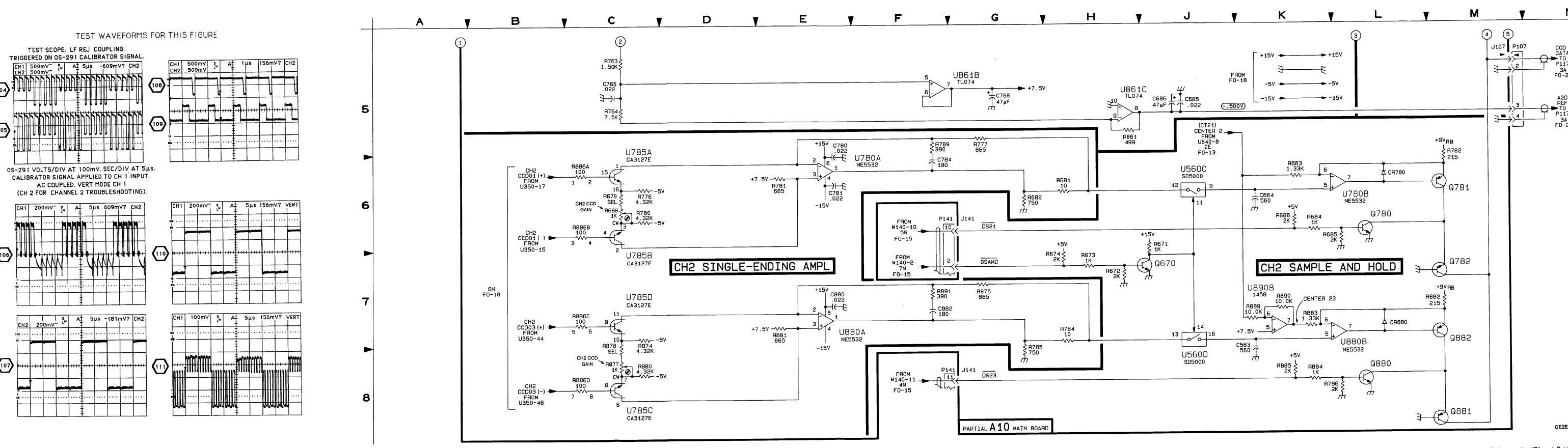

| CCD Output Schematic                                                     | FP-81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

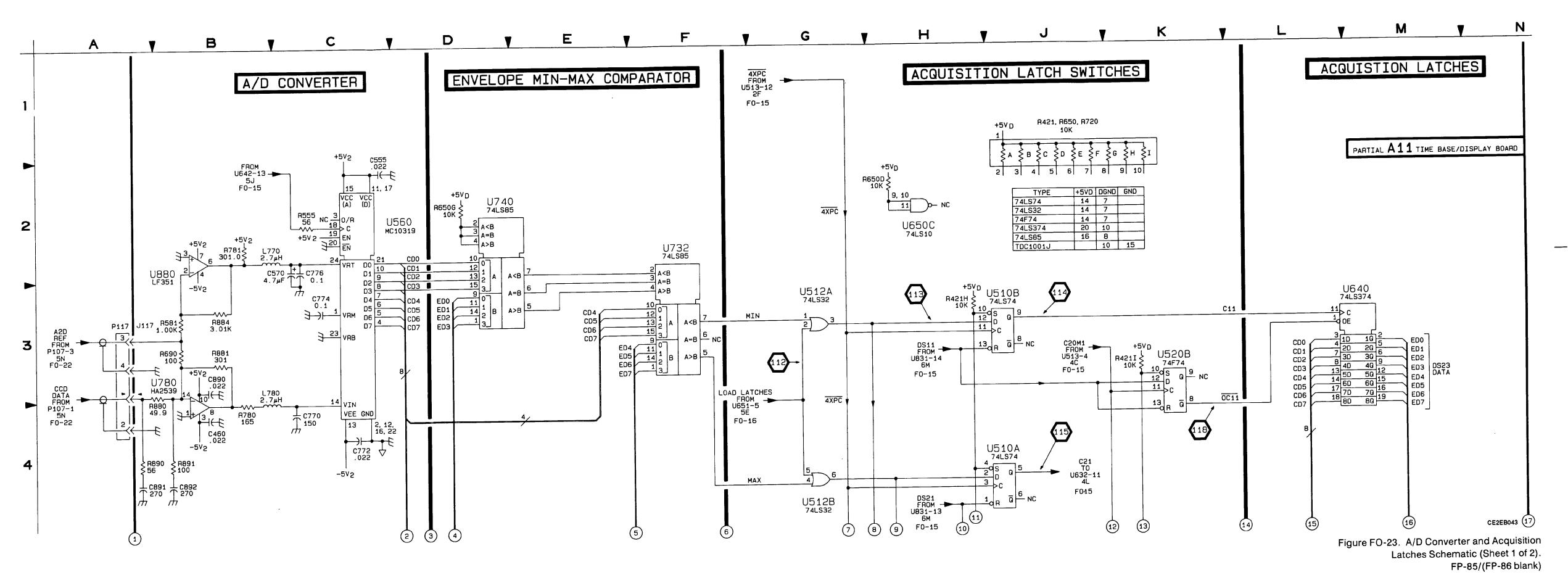

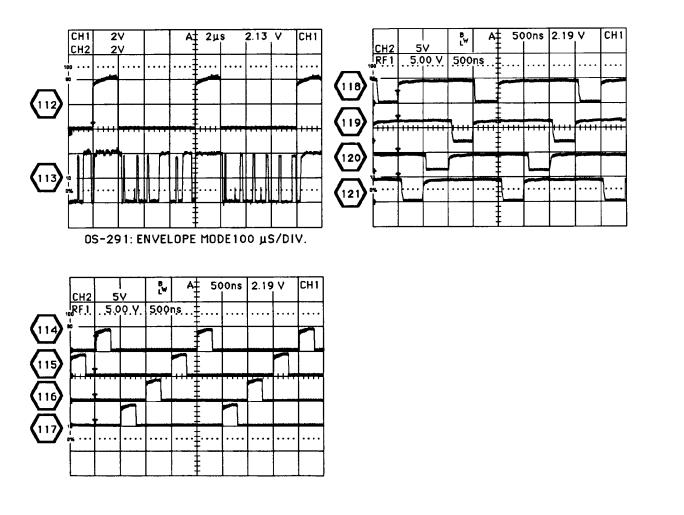

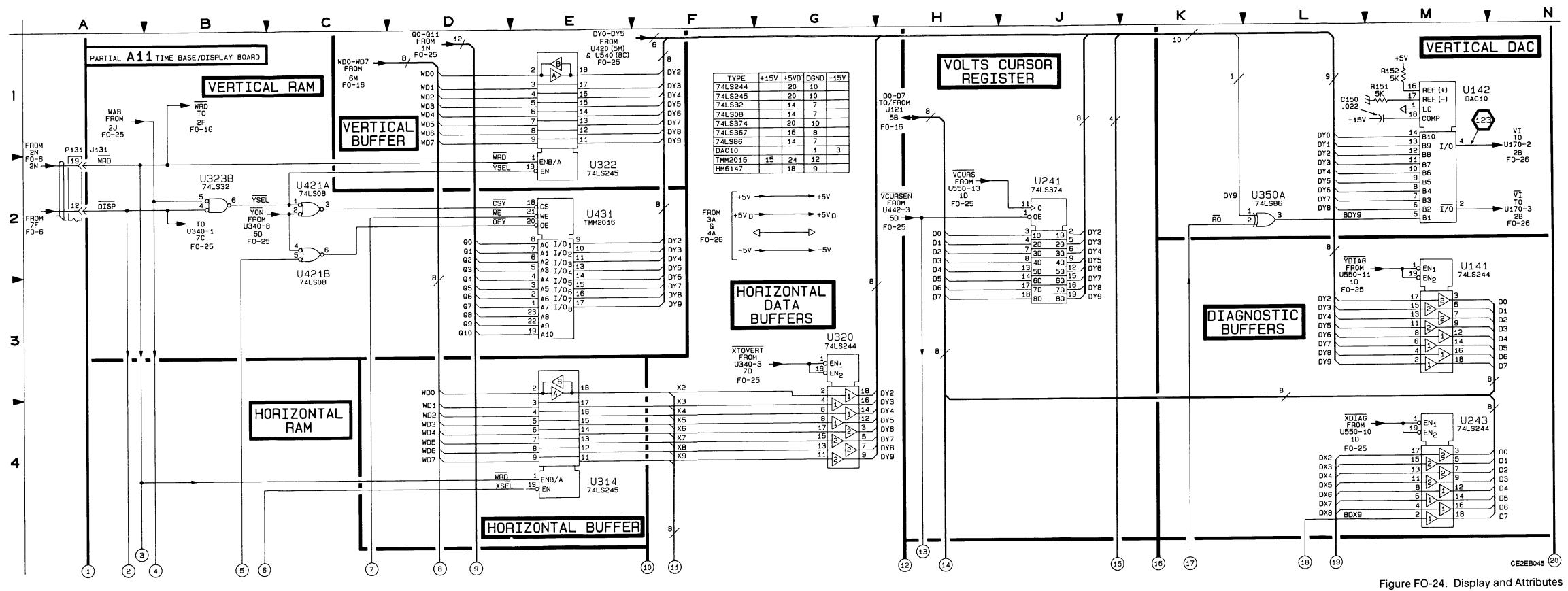

| A/D Converter and Acquisition Latches Schematic                          | FP-85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

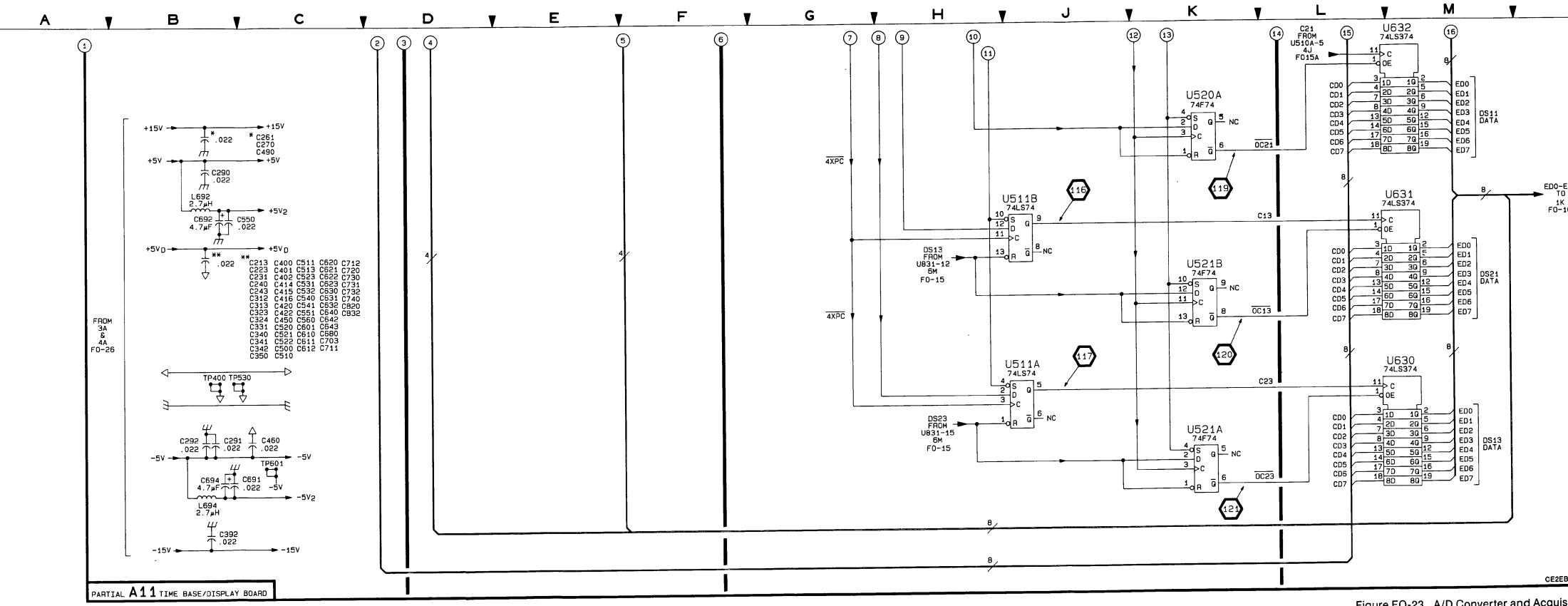

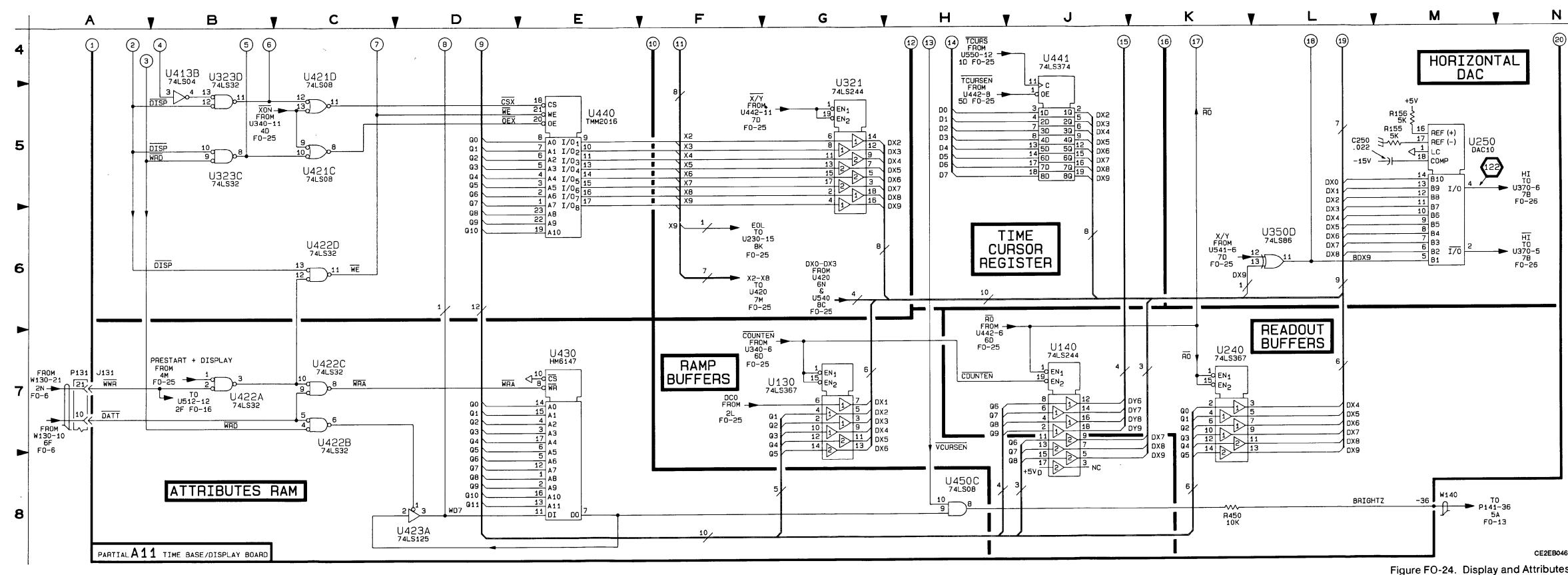

| Display and Attributes Memory Schematic                                  | FP-89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

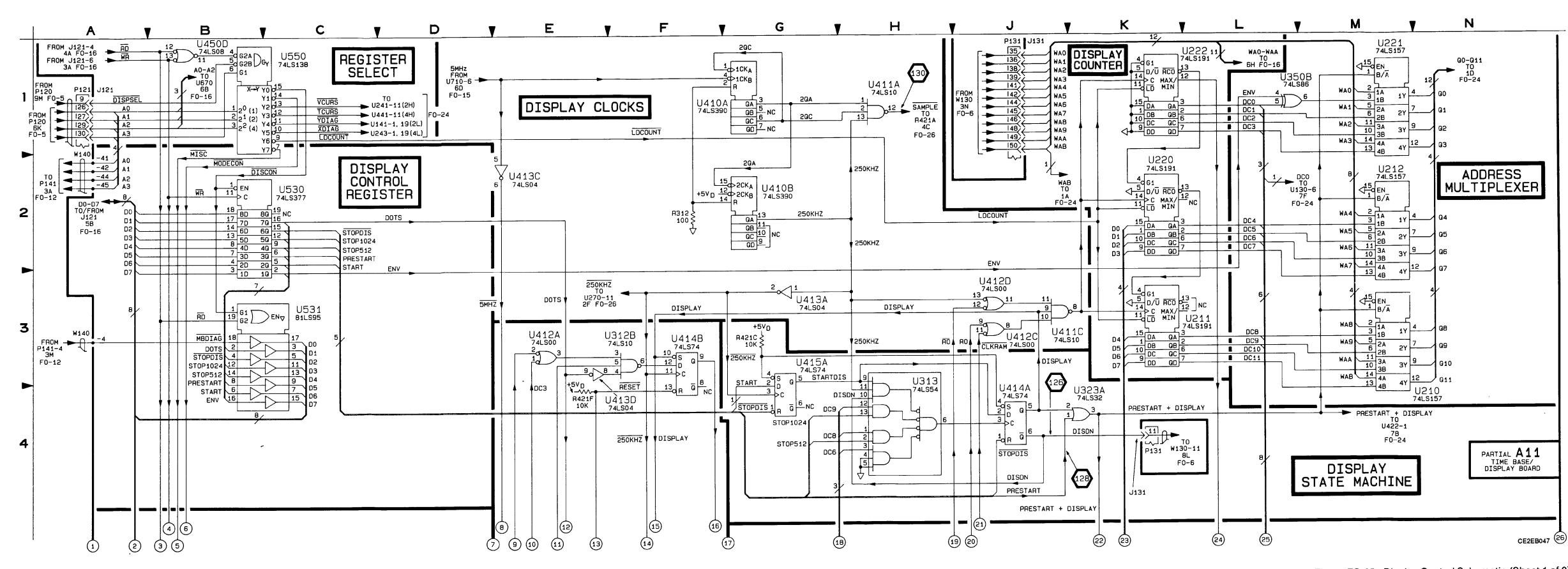

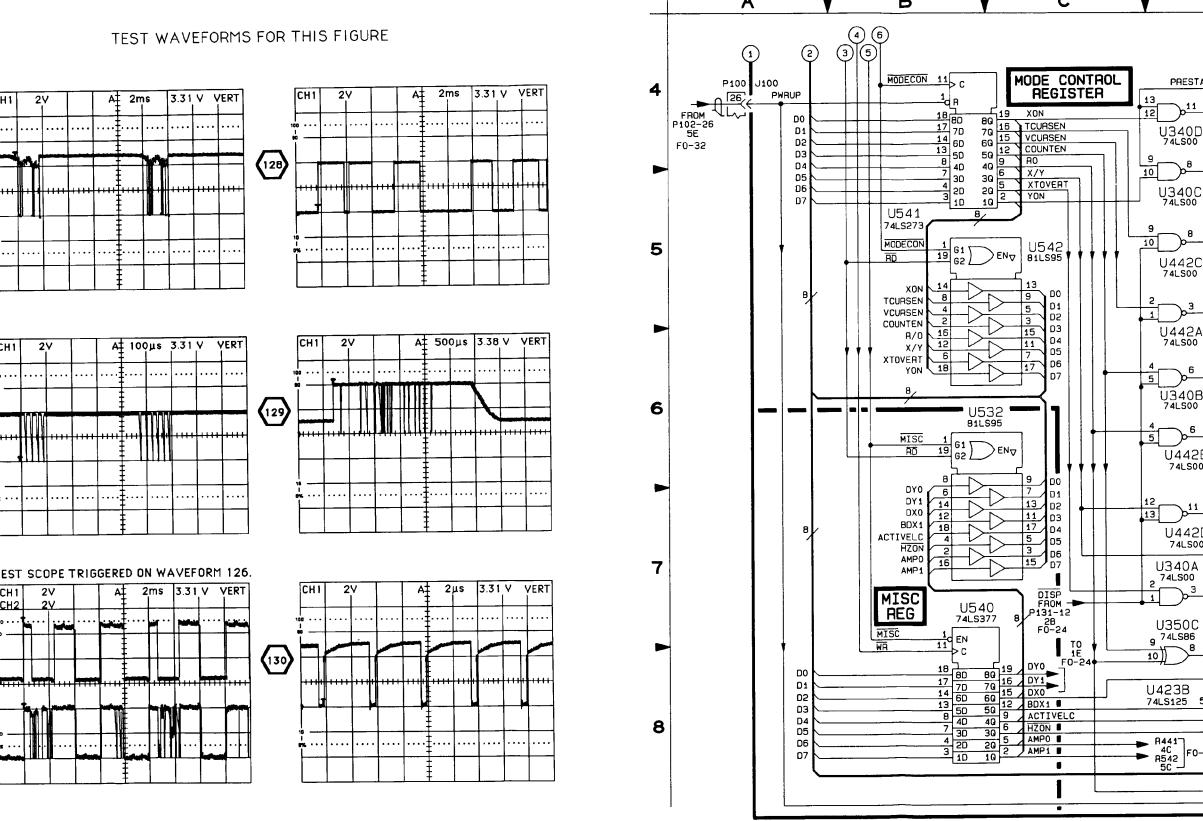

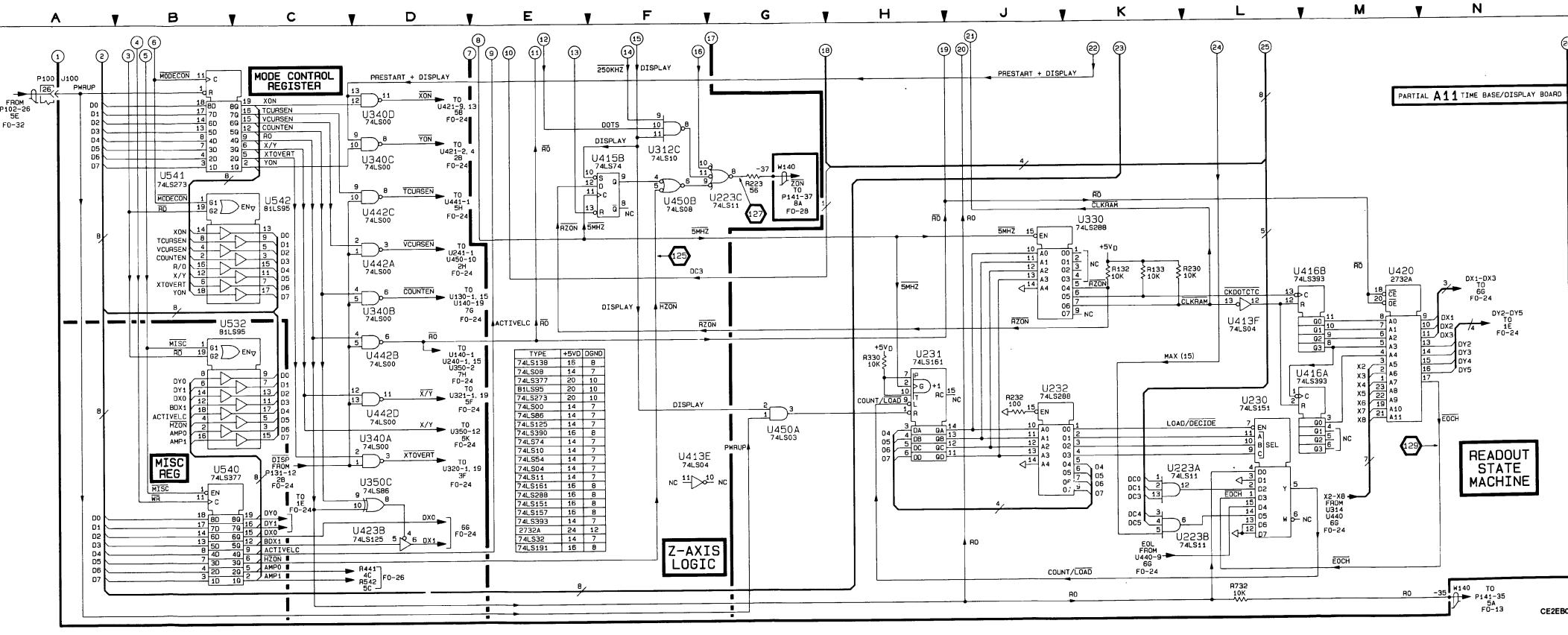

| Display Control Schematic                                                | FP-93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

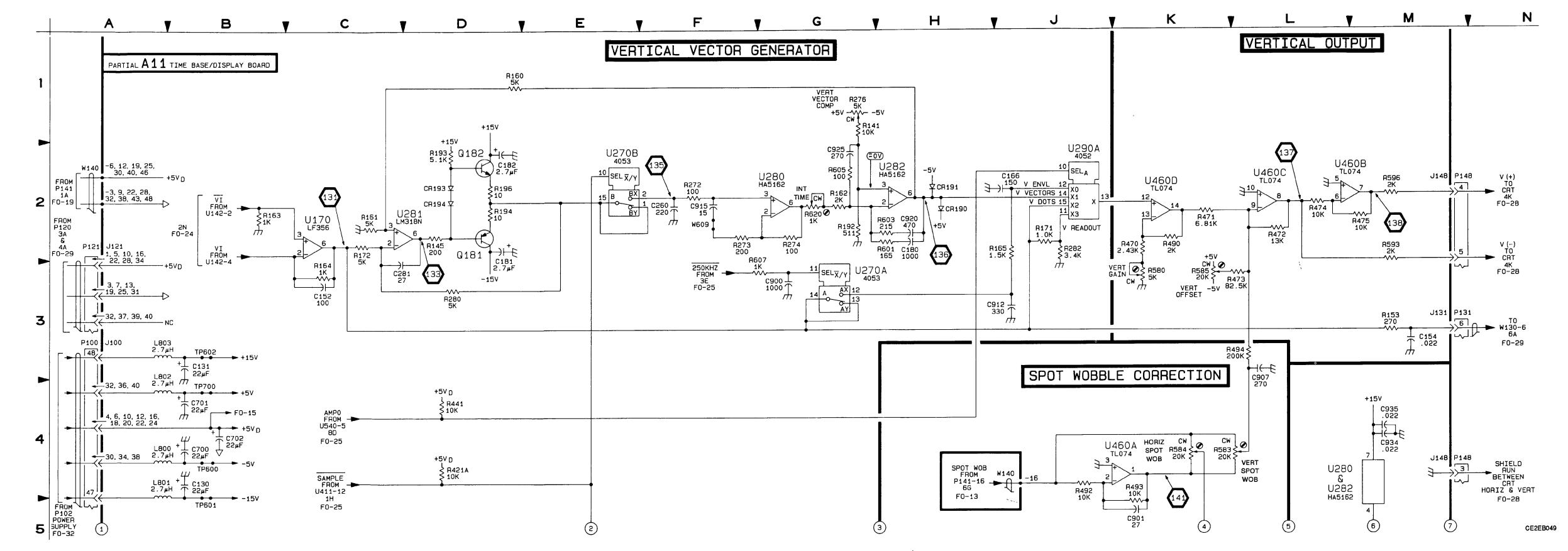

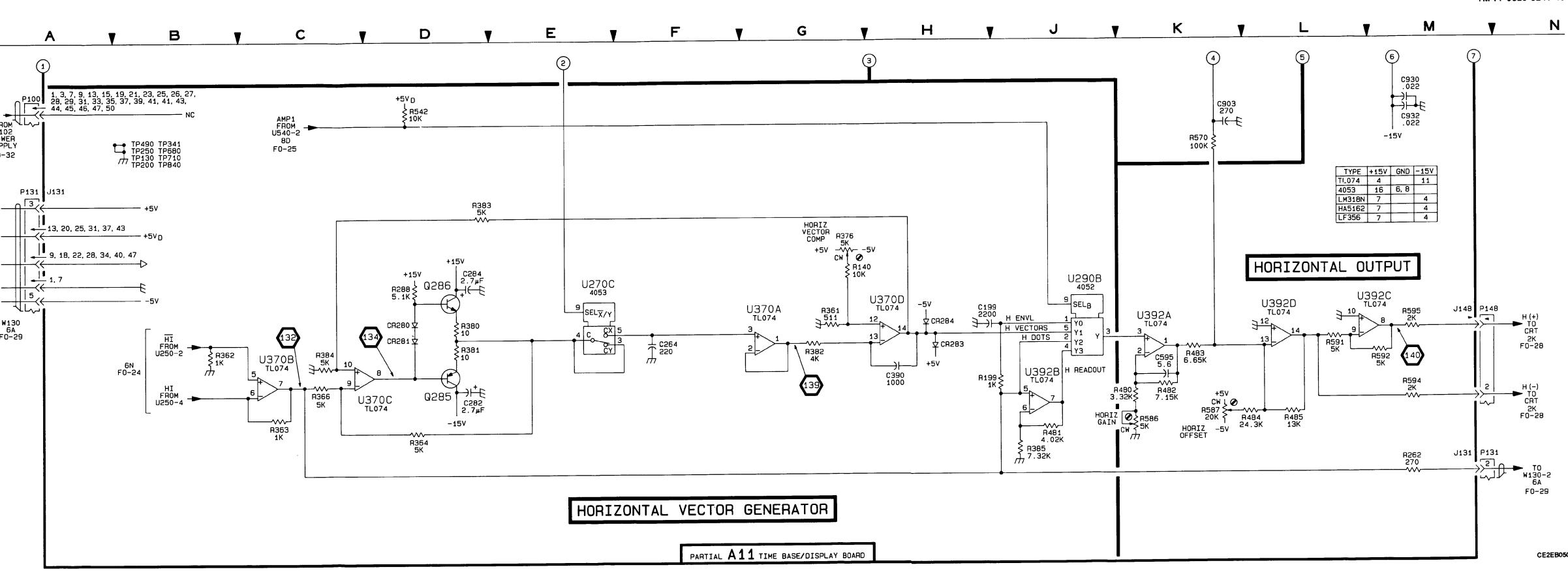

| Display Output Schematic                                                 | FP-97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

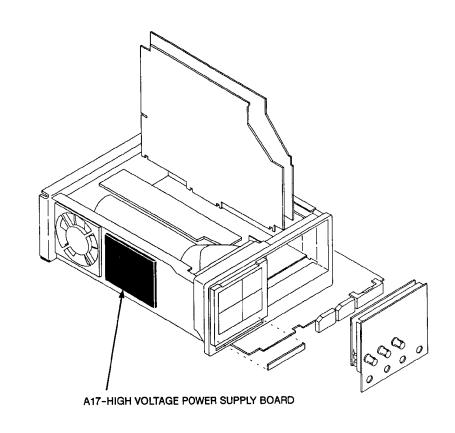

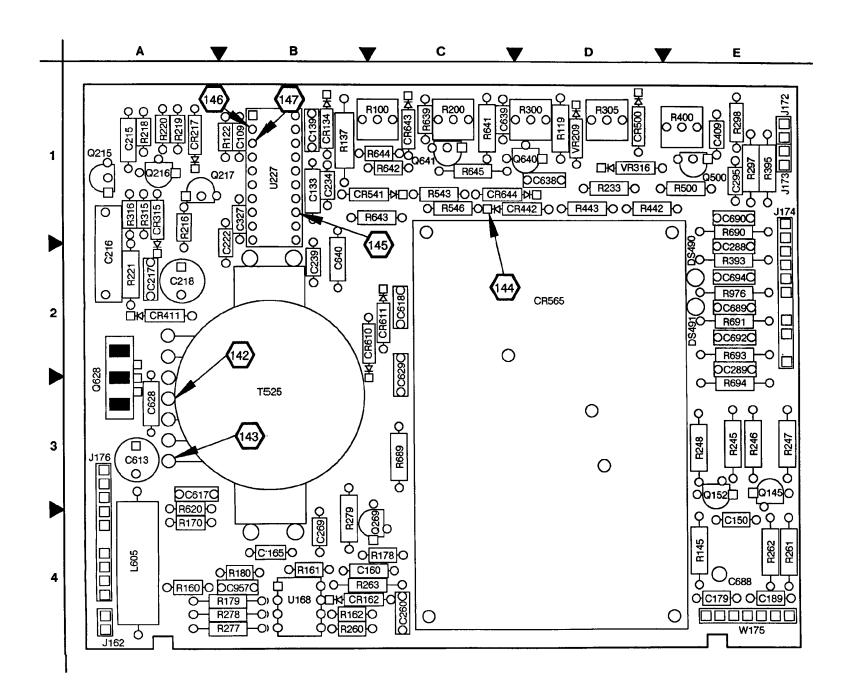

| A17 High Voltage Board Component Locator                                 | FP-103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

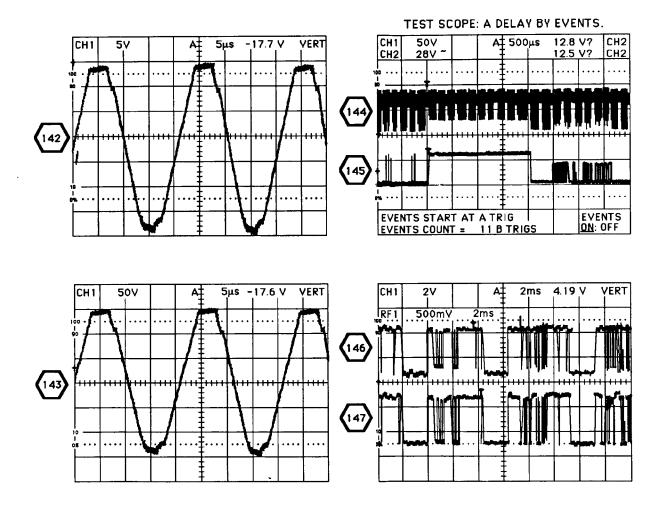

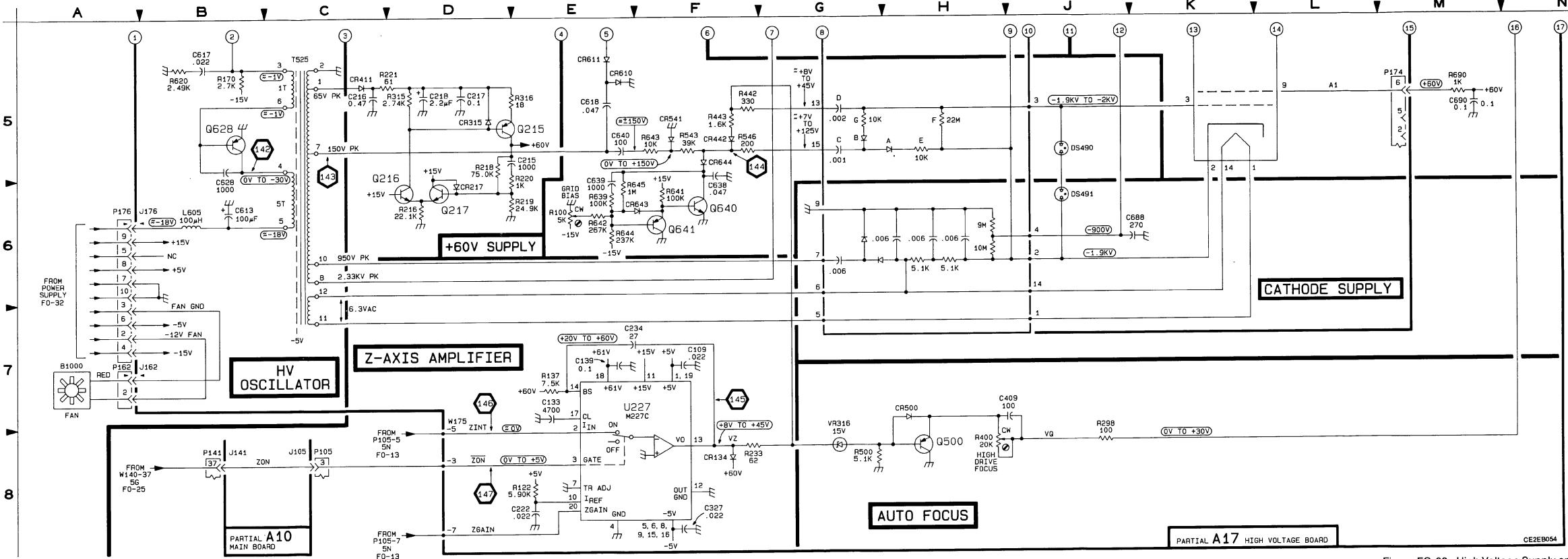

| High Voltage Supply and CRT Schematic                                    | FP-105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

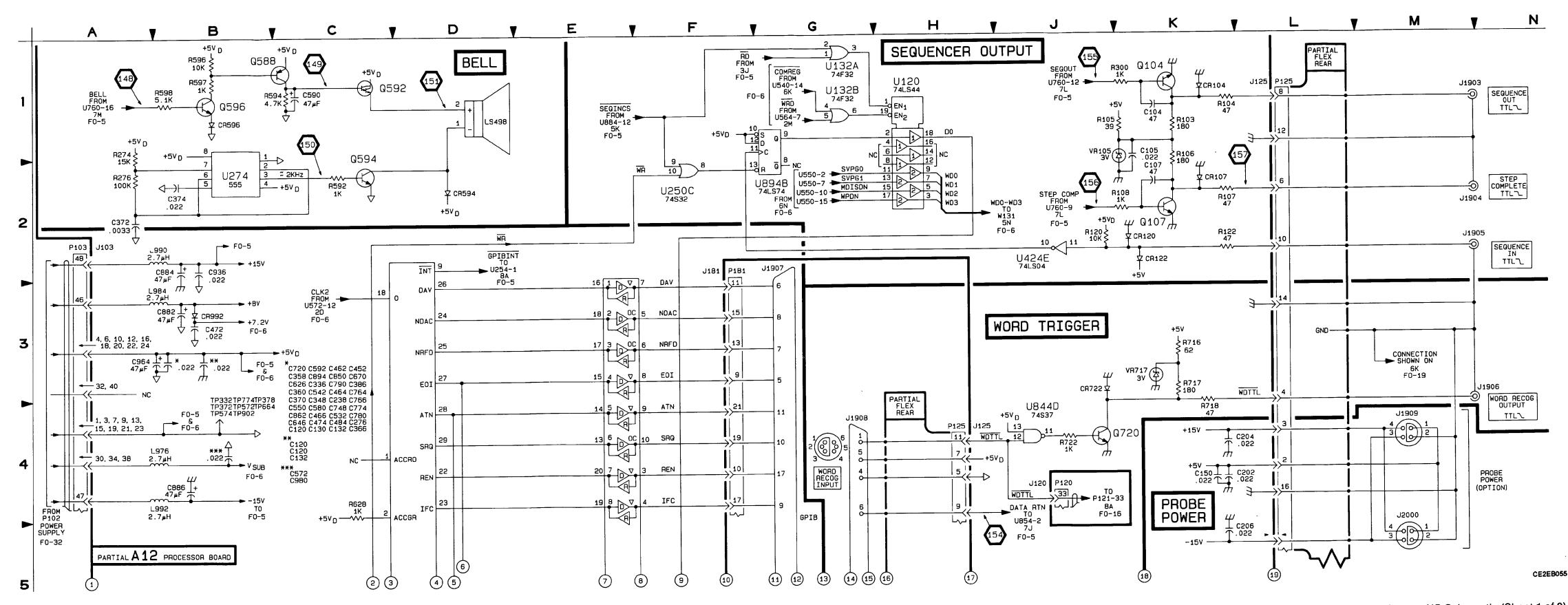

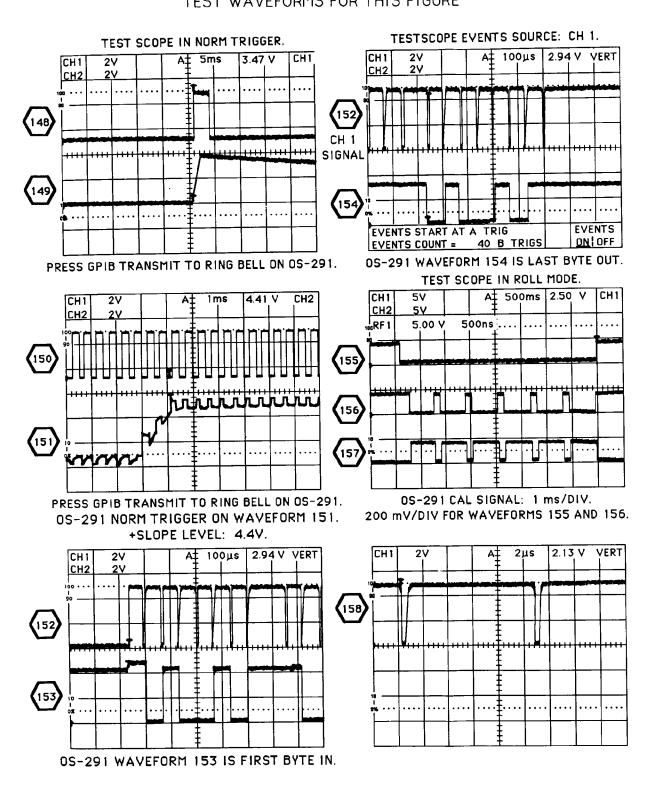

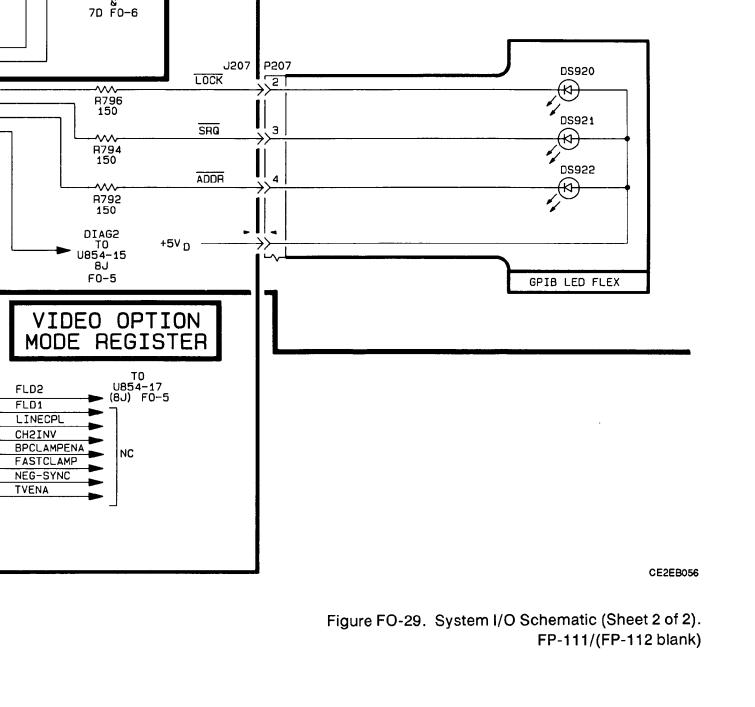

| System I/O Schematic                                                     | FP-109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

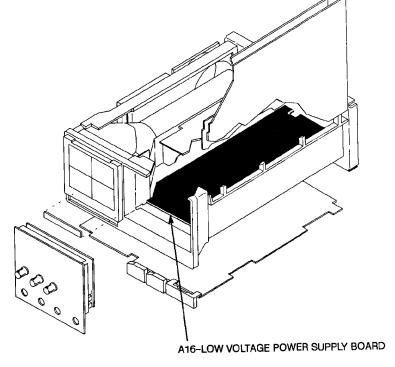

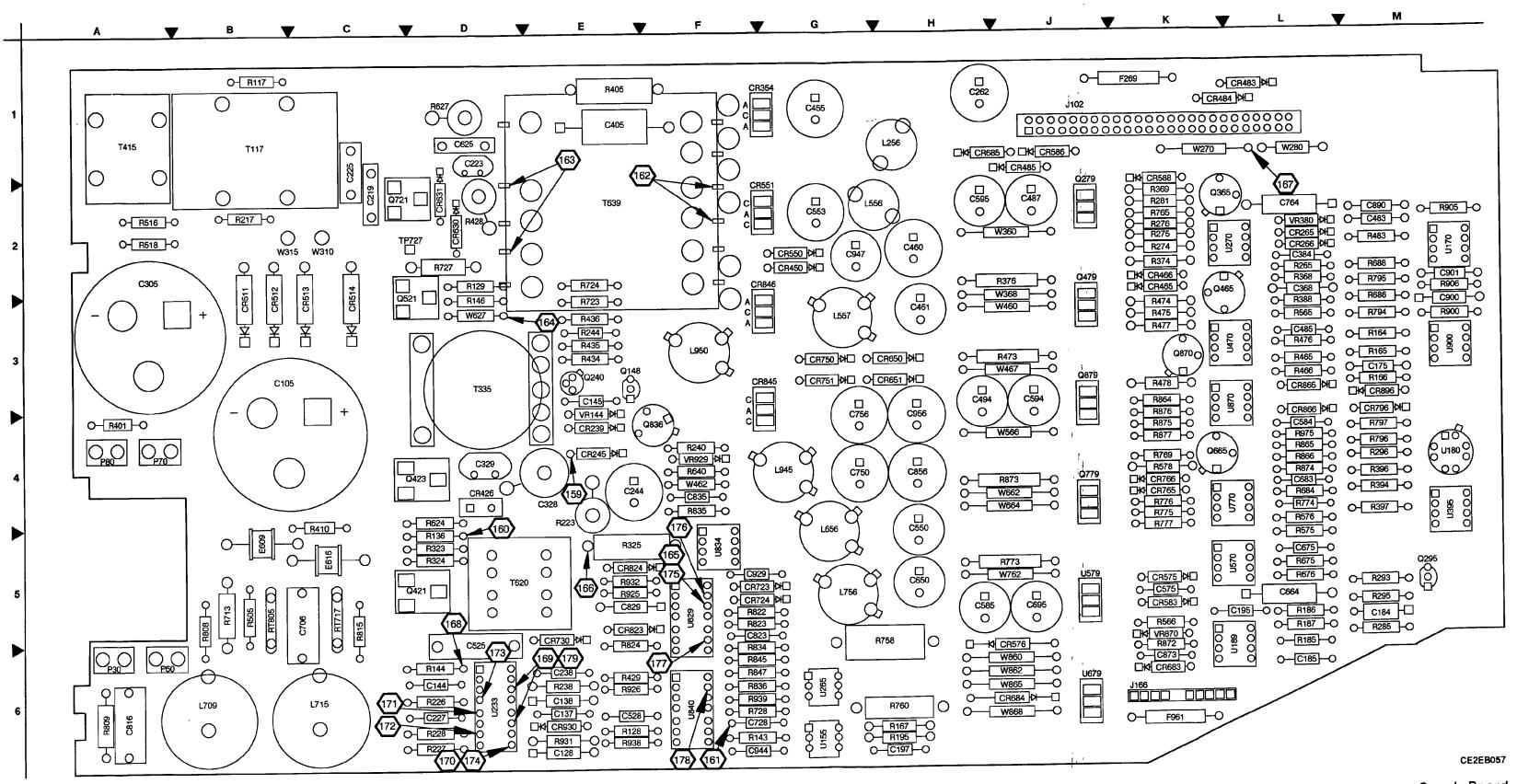

| A16 Low Voltage Power Supply Board Component Locator                     | FP-113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

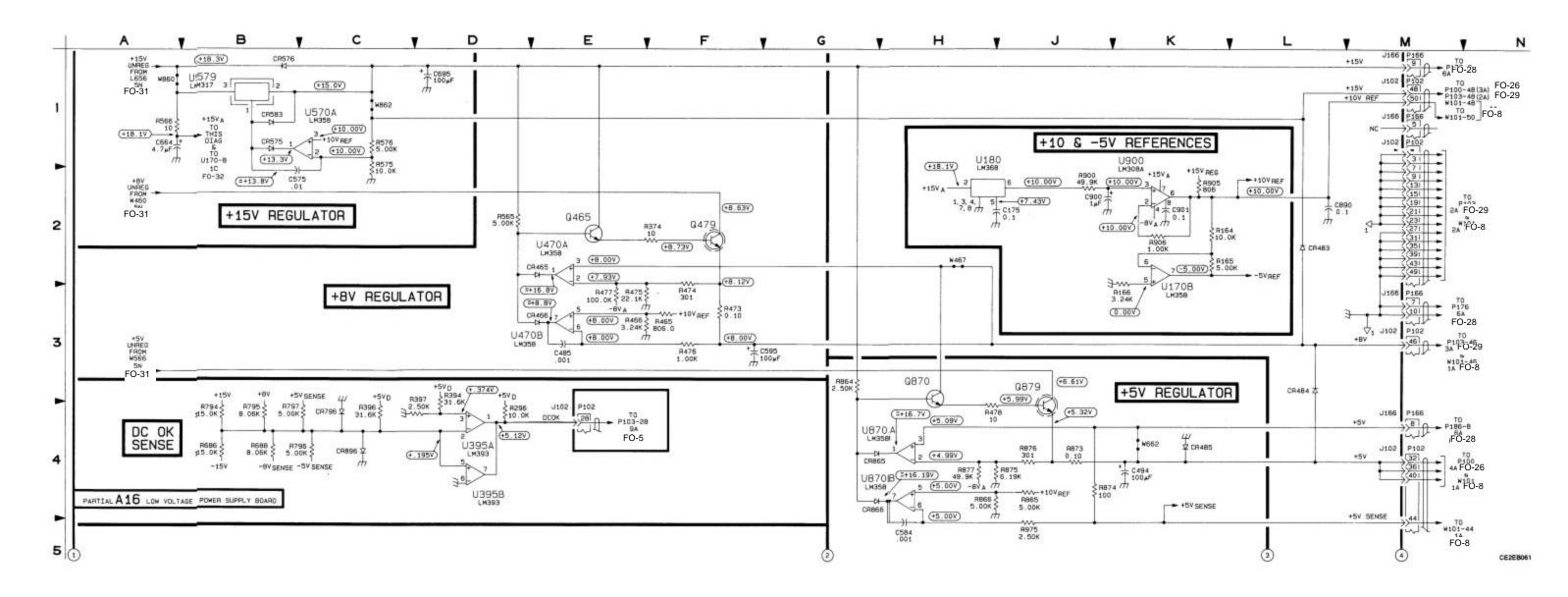

| Low Voltage Power Supply Schematic                                       | FP-115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Low Voltage Regulators Schematic                                         | FP-121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

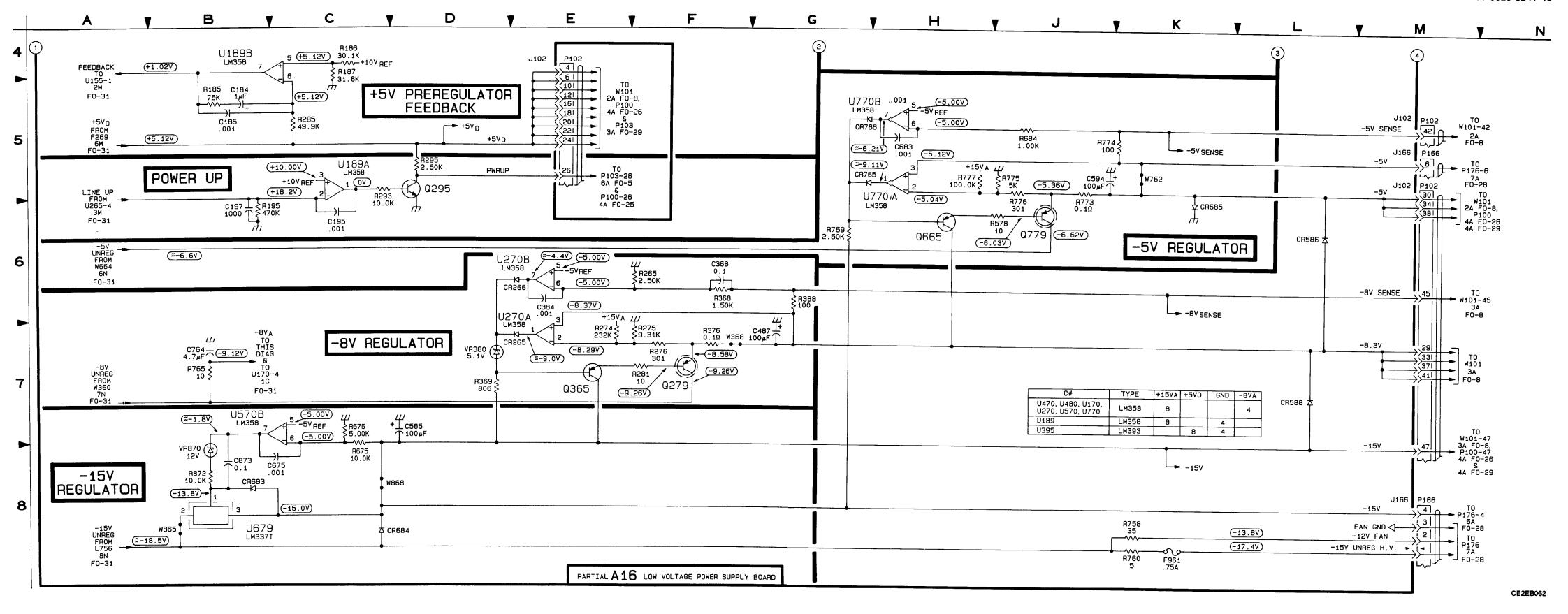

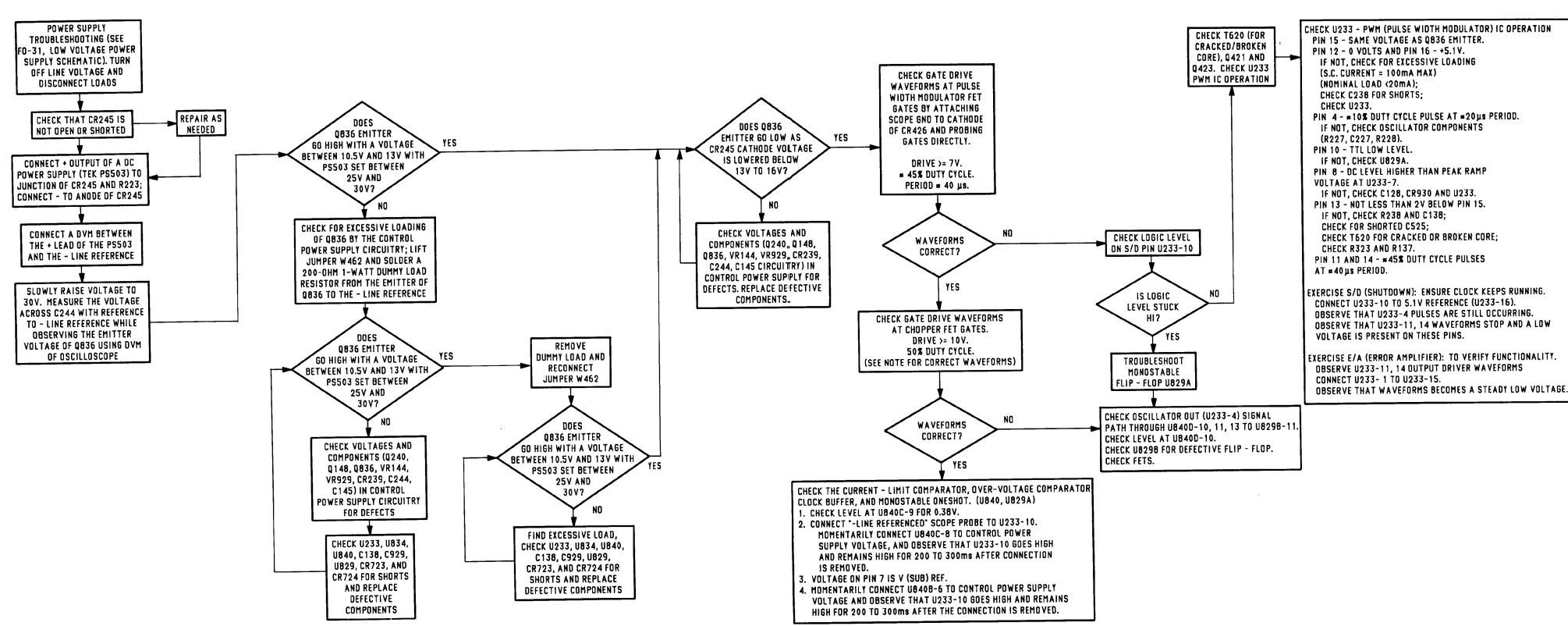

| Power Supply Troubleshooting                                             | FP-125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

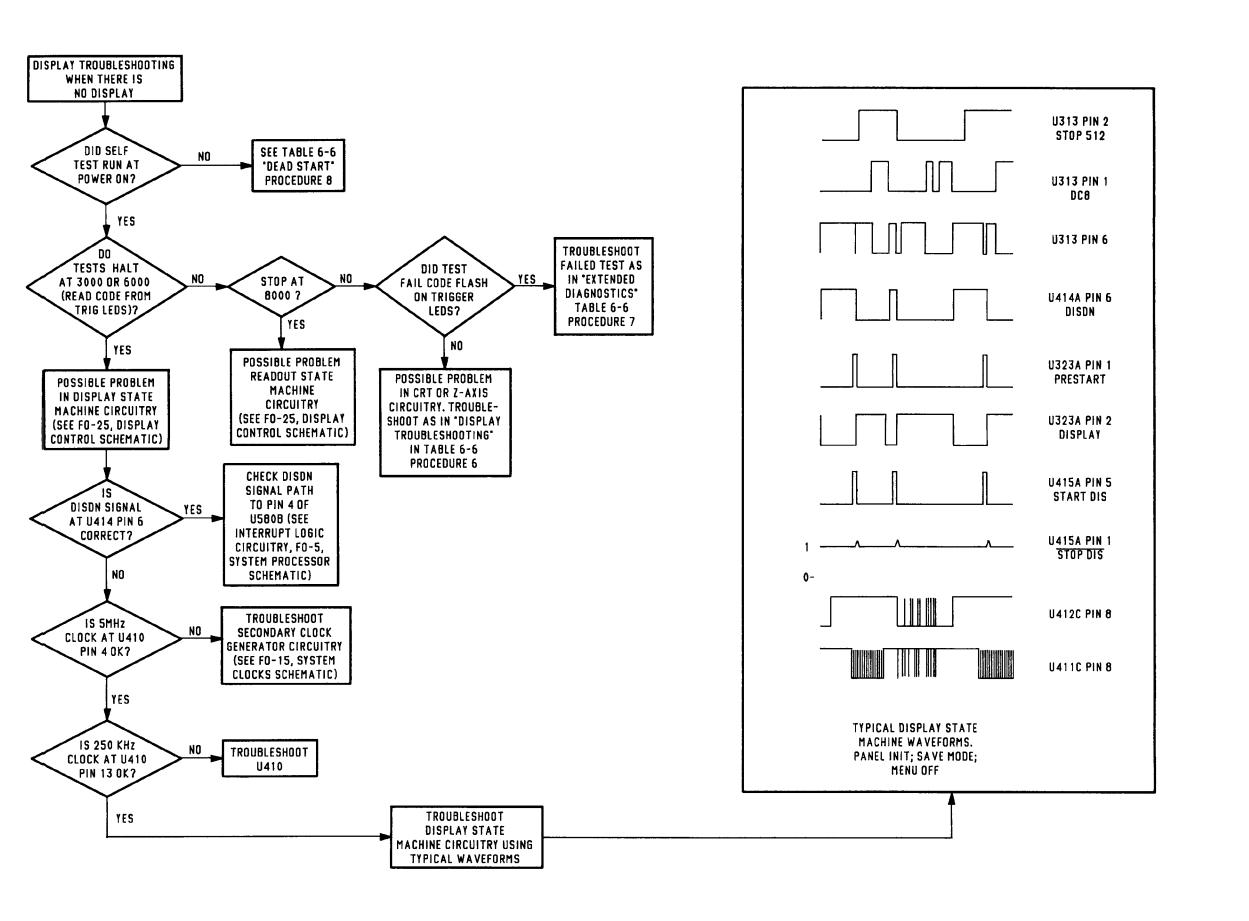

| Display Troubleshooting                                                  | FP-127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

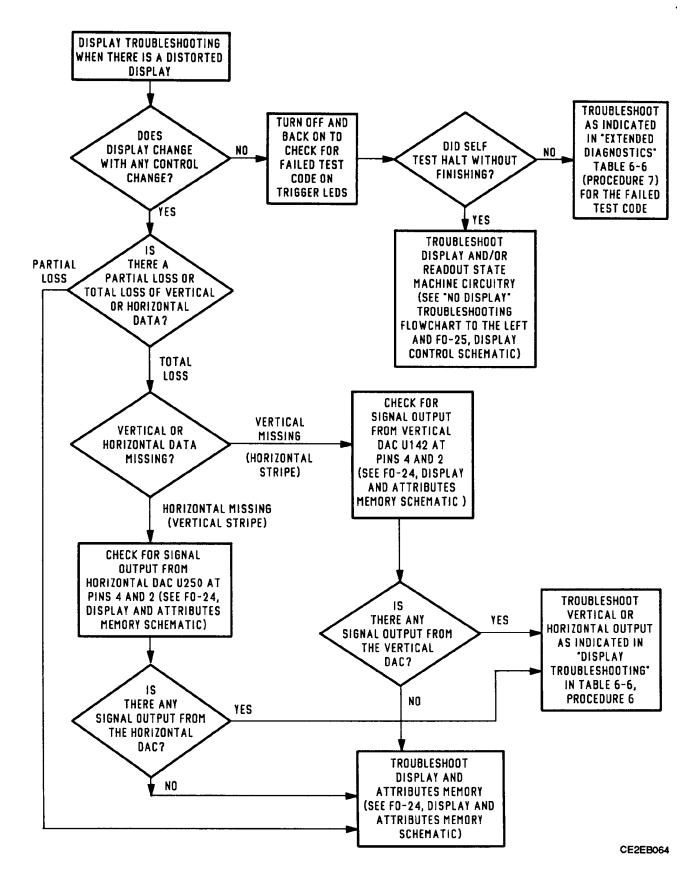

| System Clock Troubleshooting                                             | FP-129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                          | A12 Processor Board Component Locator System Processor Schematic Waveform Processor Schematic A13 Side Board Component Locator Front Panel Processor Schematic A14 Front Panel Board and A18 Scale Illumination Board Component Locator Tront Panel Schematic A10 Main Board Component Locator Acquisition Control Registers and System DAC Schematic Auxiliary Front Panel and System DAC Schematic Auxiliary Front Panel and System DAC Schematic All Time Base/Display Board Component Locator System Clocks Schematic Time Base Controller and Acquisition Memory Schematic Attenuators and Preamps Schematic Peak Detectors and CCD/Clock Drivers Schematic Triggers and Phase Clocks Schematic Jitter Correction Ramps Schematic Trigger Holdoff, Jitter Counters and Calibrator Schematic CCD Output Schematic A/D Converter and Acquisition Latches Schematic Display and Attributes Memory Schematic Display Control Schematic Display Control Schematic Display Control Schematic System I/O Schematic System I/O Schematic System I/O Schematic Low Voltage Power Supply Board Component Locator Low Voltage Power Supply Schematic Low Voltage Regulators Schematic Power Supply Troubleshooting Display Troubleshooting |

## LIST OF TABLES

| Number | Title                                                                           | Page |

|--------|---------------------------------------------------------------------------------|------|

| 1-1    | Electrical, Environmental, and Mechanical Characteristics                       | 1-4  |

| 3-1    | Host Memory-Mapped I/O                                                          | 3-19 |

| 3-2    | Processor Control Register Functions                                            | 3-20 |

| 3-3    | Processor Miscellaneous Output Register (PMISCOUT) Functions                    | 3-20 |

| 3-4    | Waveform Processor Address Decoding                                             | 3-24 |

| 3-5    | Trigger Logic ArrayAddresses (6080h-6087h)                                      | 3-48 |

| 3-6    | REF4/5 Frequency for Each SEC/DIV Setting                                       | 3-50 |

| 3-7    | Phase Clock Array Control Lines (CC3 through CCO)                               | 3-51 |

| 3-8    | Holdoff Delay Range for Current Source vs Charging Capacitor Combinations       | 3-54 |

| 3-9    | Side Board Address Decoding                                                     | 3-56 |

| 4-1    | Cross Reference for Test Equipment                                              | 4-2  |

| 4-2    | Accuracy Limits CH 1 and CH 2 CURSOR VOLTS Readout and A and B TRIGGER Readouts | 4-8  |

| 4-3    | Minimum Display Level for CH 1 or CH 2 Triggering (in divisions)                | 4-15 |

| 4-4    | Minimum Signal Level for EXT1 or EXT 2 Triggering (in millivolts)               | 4-17 |

| 6-1    | Relative Susceptibility to Static-Discharge Damage                              | 6-3  |

| 6-2    | External Inspection Checklist                                                   | 6-4  |

| 6-3    | Internal Inspection Checklist                                                   | 6-5  |

| 6-4    | Power Supply Voltage and Ripple Limits                                          | 6-10 |

| 6-5    | Maintenance Aids                                                                | 6-12 |

| 6-6    | OS-291/G Troubleshooting Procedures                                             | 6-34 |

| 6-7    | INIT PANEL State                                                                | 6-97 |

# Section 0 INTRODUCTION

### SCOPE

This manual contains instructions for the General Support Maintenance of the Oscilloscope OS-291/G. Throughout this manual, the oscilloscope is referred to as the instrument, the Tektronix 2430A, or the OS-291/G.

## CONSOLIDATED INDEX OF ARMY PUBLICATIONS AND BLANK FORMS

Refer to the latest issue of DA PAM 25-30 to determine whether there are new additions, changes, or additional publications pertaining to this equipment.

## MAINTENANCE FORMS, RECORDS, AND REPORTS

- a. Report of Maintenance and Unsatisfactory Equipment. Department of the Army forms and procedures used for equipment maintenance will be those prescribed by DA PAM 738-750 as contained in Maintenance Management Update. Marine Corps maintains forms and procedures as prescribed by TM4700-15/1.

- b. Report of Item and Packaging Deficiencies. Fill out and forward SF 364 (Report of Discrepancy (ROD)) as prescribed in AR 735-11-2/DLAR 4140.55/SECNAVINST 4355.18/AFR 400-54/MCO 4430.3J.

- c. Transportation Discrepancy Report (TDR) (SF 361). Fill out and forward Transportation Discrepancy Report (TDR) (SF 361) as prescribed in AR 55-37/NAVSUPINST 4610.33C/AFR 75-18/MCO P4610.19D DLAR 4500.15.

# REPORTING EQUIPMENT IMPROVEMENT RECOMMENDATIONS (EIR)

- a. Army. If your OS-291/G needs improvement, let us know. Send us an EIR. You, the user, are the only one who can tell us what you don't like about your equipment. Let us know why you don't like the design or performance. Put it on an SF 368 (Product Quality Deficiency Report). Mail it to us at: Commander, US Army Communications Electronics Command and Fort Monmouth, ATTN: AM-SEL-PA-MA-D, Fort Monmouth, New Jersey 07703-5000. We'll send you a reply.

- b. Marine Corps Users. QDR shall be reported on SF 368 in accordance with MCO P4855.10, Product Quality Deficiency Report Manual. Submit to Commanding General, Marine Corps Logistics Base (Code 856), Albany, Georgia 31704-5000.

### ADMINISTRATIVE STORAGE

Administrative storage of equipment issued to and used by Army activities will have preventive maintenance performed in accordance with PMCS charts before storing. When removing the equipment from administrative storage the PMCS should be performed to ensure operational readiness.

## DESTRUCTION OF ARMY ELECTRONICS MATERIEL TO PREVENT ENEMY USE

Destruction of Army electronics materiel to prevent enemy use shall be in accordance with TM 750-244-2.

Figure 1-1. Oscilloscope OS-291/G.

## Section 1 SPECIFICATION

### INTRODUCTION

The Tektronix 2430A Digital Oscilloscope is a portable, dual-channel instrument with a maximum digitizing rate of 100 Megasamples per second. The scope is capable of simultaneous acquisition of Channel 1 and Channel 2 input signals. It has a real-time useful storage bandwidth of 40 MHz for single-event acquisitions, with an equivalent-time bandwidth of 150 MHz when repetitive acquisitions are acquired. Since both channels are acquired simultaneously, the XY display is available to full bandwidth.

The instrument is microprocessor controlled and menu driven, displaying at the top of the screen alphanumeric CRT readouts of the vertical and horizontal scale factors, trigger levels, trigger sources and cursor measurements. Menus, displayed at the bottom of the CRT display, are used by the operator to select the operating mode.

A user makes decisions as to what operation and mode setup the instrument must have to make the measurement wanted and then selects the proper functions using a combination of front-panel buttons and the displayed menu.

Five menu buttons mounted on the CRT bezel are used to make selections from the entry choices displayed. The top line of the menu display usually contains the menu title, and the bottom line labels the buttons with the control functions they select. The selection is made (indicated by an underscoring of the menu label in the display) when the bezel button below the selected function is pressed. The menus, system operating modes, and auxiliary functions are described in chapter 2 of the Operators and Unit Maintenance manual.

## **VERTICAL SYSTEM**

The two vertical channels have calibrated deflection factors from 2 mV to 5 V per division in a 1-2-5 sequence of 14 steps. Use of coded probes having attenuation factors of 1X, 10X, 100X, and 1000X extends the minimum sensitivity to 5,000 V per division (with the 1000X probe) and the maximum sensitivity to 200  $\mu V$  per division (using a 1X probe in SAVE or AVERAGE expanded mode).

VOLTS/DIV readouts are automatically switched to display a correct scale factor when properly coded probes are attached. Each channel can be separately inverted. ADD and MULT are display functions provided by the processor system.

In SAVE mode, the waveforms maybe both horizontally and vertically repositioned, expanded horizontally and vertically, added to each other, or multiplied together for either XY or YT displays.

## **HORIZONTAL SYSTEM**

Horizontal display modes of A, A INTEN, and B Delayed are available. The time base has 28 calibrated SEC/DIV settings in a 1-2-5 sequence from 5 ns per division to 5 s per division. An External Clock mode is provided that accepts clocking signals from 1 MHz to 100 MHz.

The B Trace and the intensified zone on the A INTEN Trace may be delayed by time with respect to the A trigger, and a DELAY by EVENTS function permits the A display to be delayed by a selected number of B Trigger events. In the case of DELAY by EVENTS, the B Trigger SOURCE, COUPLING, SLOPE, and LEVEL controls define the nature of the signal needed to produce events Triggering. The number of events required to satisfy the delay may beset from 1 to 65,536, with a resolution of one event. The DELTA DELAY feature produces two independently settable delayed B Traces in DELAY by TIME.

## TRIGGER SYSTEM

The trigger system of the scope provides many features for selecting and processing a signal used in triggering the acquisition system. The conventional features of SOURCE selection, Trigger LEVEL control, Trigger SLOPE, Trigger MODE, and CPLG (coupling) include enhancements not normally found in a conventional oscilloscope.

The choices of VERT, CH1 or CH2, EXT1 or EXT2, LINE, and A\*B or WORD (16-bit data word recognition) are available as SOURCE selections for triggering A Horizontal Mode acquisitions. These sources for trigger signals provide a wide range of applications involving specialized triggering requirements. Except for A\*B (A AND B) and LINE (power-source frequency), the same Trigger SOURCE selections are available for triggering B

acquisitions. The selected trigger signal is conditioned by the choice of input CPLG (coupling). These coupling selections are AC, DC, HF REJECT, LF REJECT, and NOISE REJECT. LEVEL control provides a settable amplitude (with CRT readout) at which triggering will occur, and SLOPE control determines on which slope of the triggering signal (plus or minus) the acquisition is triggered.

Trigger MODE choices are AUTO LEVEL, AUTO/ROLL, NORM (normal), and SINGLE SEQ (single sequence), for the A and A INTENSIFIED Modes, and Triggerable After Delay and Runs After Delay, for the B Mode. AUTO LEVEL provides for automatic leveling on the applied trigger signal. AUTO MODE produces an auto trigger in the event a trigger signal is either not received or not within the limits needed to produce a triggering event. When triggering conditions are met, a normal triggered display results. At SEC/DIV settings of 100 ms per division and longer, the AUTO MODE switches to ROLL. in ROLL MODE, the display is continually updated and trigger signals are disregarded.

NORM (normal) trigger MODE requires that all triggering requirements are met before an acquisition will take place. SINGLE SEQ (single sequence) MODE is a variation of the conventional single-shot displays found on many previous oscilloscopes. In SINGLE SEQ, a single complete acquisition is done on all called-up VERTICAL MODES. Since an acquisition depends on the acquisition mode in effect, many of the scope operating features are altered in SINGLE SEQ.

The user has a choice of trigger points within the acquired waveform record by selecting the amount of pretrigger data displayed. The trigger location in the record is selectable from a choice of five pretrigger lengths beginning atone-eighth of the record length and increasing to seven-eighths of the record length. A record trigger position is independently selectable for both A and B acquisitions. Additional trigger positions in the record are selectable via the GPIB interface commands.

## **CURSOR MEASUREMENTS**

Time and Voltage cursors are provided for making parametric measurements on the displayed waveforms. Time may be measured either between the cursor positions (DELTA TIME) or between a selected cursor and the trigger point of an acquired waveform (ABSO-LUTE). Time cursor readouts are scaled in seconds, degrees, or percentage values. The I/TIME cursors may be scaled in hertz (Hz), degrees, or percentage.

Voltage cursor measurements on a waveform display can be selected to read either the voltage difference

between the cursor positions or the absolute voltage position of a selected cursor with respect to ground. The volts measurement readouts may be scaled in units of volts, decibels (dB), or percent. The Voltage cursors and Time cursors may also be coupled to track together (V@T and SLOPE) and assigned to a particular waveform for ease in making peak-to-peak and slope waveform measurements. The units for V@T may be volts, percent, or dB; SLOPE may have units of slope (VOLTS/SEC), percent (VOLTS/VOLT), or dB.

## WAVEFORM ACQUISITION

Waveforms may be acquired in different modes, depending on the measurement requirements. The acquisition modes of NORMAL, ENVELOPE, and AVG (averaging) provide the user with a wide range of measurement adaptability. NORMAL mode provides a continuous acquisition producing a "live" waveform display similar to that seen with an analog oscilloscope. AVG (averaging) mode is especially useful for improving the signal-to-noise ratio of the displayed waveform. Small amplitude signals masked by noise become easily visible for making measurements and analysis by averaging from 2 to 256 acquisitions for removing uncorrelated noise.

Equivalent-time sampling, used for NORMAL and AVG acquisition of recurring periodic signals, extends the useful storage bandwidth to 150 MHz when the REPETITIVE mode is on. Randomly acquired data points taken from aperiodic signal are used to fill the complete record of the signal waveform display. Depending on the SEC/DIV setting, as few as 10 samples (at 5 ns/DIV) or as many as 409 (at 200 ns/DIV) samples maybe obtained on each trigger event. The user sees the waveform display build up as dots until the entire 1024 data point record is filled.

ENVELOPE mode saves the maximum and minimum data-point values over a selected number of acquisitions from 1 to 256 plus CONT (continuous). The display presents a visual image of the amount of change (envelope) that occurs to a waveshape during the accumulated acquisitions. Frequency, phase, amplitude, and position changes are easily identified when acquiring in ENVELOPE mode. The glitch-catching capability of ENVELOPE mode can capture single-event pulses as narrow as 2 ns at the slowest SEC/DIV setting of 5 seconds per division.

Horizontally, the record length of acquired waveforms is 1024 data points (512 max/min pairs in ENVELOPE mode), of which 500 make up a one-screen display (50 data points per division for 10 divisions). The entire record may be viewed by using the Horizontal POSITION control to position any portion of the record within the viewing area.

## STORAGE AND I/0

Acquired waveforms may be saved in any of four REF (reference) waveform nonvolatile memories. Any or all of the saved reference waveforms may be displayed for comparison with the waveforms being currently acquired. The source and destination of waveforms to be saved may be user designated. Assignment can be made to save either channel 1 or channel 2 (or the results of an addition or multiplication of the two channels) to any REF memory or to move a stored reference from one REF memory to another. Reference waveforms may also be written into a REF memory location via the GPIB interface.

The scope is fully controllable and capable of sending and receiving waveforms via the standard equipped GPIB interface. This feature makes the instrument ideal for making automated measurements in a production or research and development environment that calls for repetitive data taking. Self-calibration and self-diagnostic features built into the scope to aid in fault detection and servicing are also accessible via commands sent from the GPIB controller.

Another standard feature is the DEVICES setting for GPIB Interface control. This feature allows the user to output waveforms (and other on-screen information) to either a HP® Graphics Printer or Plotter from the scope front-panel, providing a way to obtain hard-copies of acquired waveforms without putting the scope into a system controller environment.

## **EXTENDED FEATURES**

There are several other features incorporated into this instrument designed to make it more usable, namely, the HELP, AUTOsetup, MEASURE, and AutoStep Sequencer features.

**HELP:** The HELP function can be used to display operational information about any front-panel control. When HELP mode is in effect, manipulating almost any front-panel control causes the scope to display information about that control. When HELP is first invoked, an introduction to HELP is displayed on screen.

**AUTOsetup:** The AUTOsetup function is used to automatically setup the scope for a viewable display based on the input signal. The user can specify the waveform characteristic the display is optimized for (front-edge, period, etc.) from a menu displayed upon executing AUTOsetup.

**MEASURE:** MEASURE automatically extracts parameters from signal input to the scope. In the SNAPSHOT mode, 20 different waveform parameters are extracted and displayed for a single acquisition. In the continuous extraction mode, up to four parameters are extracted continuously as the instrument continues to acquire.

AutoStep Sequencer (PRGM): With AutoStep, the user can save single front-panel setups or sequences of setups and associated flow control and Input/Output actions for later recall. If MEASURE and/or OUTPUT are saved as part of these setups they can be used for automatic parameter extraction and data printout. 100 to 800 front-panel setups (depending on complexity) can be stored in one or more sequences.

The descriptions of these four features are found in Chapter 2 of the Operators and Unit Maintenance manual for this instrument.

For part numbers and further information about standard accessories and a list of the optional accessories, refer to the Unit, Direct Support, and General Support Repair Parts and Special Tools List for Oscilloscope OS-291/G.

### PERFORMANCE CONDITIONS

Electrical, environmental, and mechanical characteristics are listed in Table 1-1.

Electrical characteristics apply when the scope has been calibrated at an ambient temperature between + 20±°C and + 30°C, has had a warmup period of at least 20 minutes and is operating at an ambient temperature between -15°C and + 55°C (unless otherwise noted).

The scope meets the environmental requirements of MIL-T-28800C for Type III, Class 3, Style D equipment, with the humidity and temperature requirements defined in paragraphs 3.9.2.2, 3.9.2.3, and 3.9.2.4.

## RECOMMENDED ADJUSTMENTS SCHEDULE

For optimum performance to specification, the internal SELF CAL should be done:

- a. If the operating temperature is changed by more than 50°C since the last SELF CAL was performed.

- b. Immediately before making measurements requiring the highest degree of accuracy.

Table 1-1

Electrical, Environmental, and Mechanical Characteristics

| Characteristics                                           | Performance Requirements        |

|-----------------------------------------------------------|---------------------------------|

| W                                                         | VEIGHT AND DIMENSIONS           |

| Weight                                                    | 28.1 lbs (12.8 kg).             |